AD7226

rev. 一个

–6–

接口 逻辑 信息

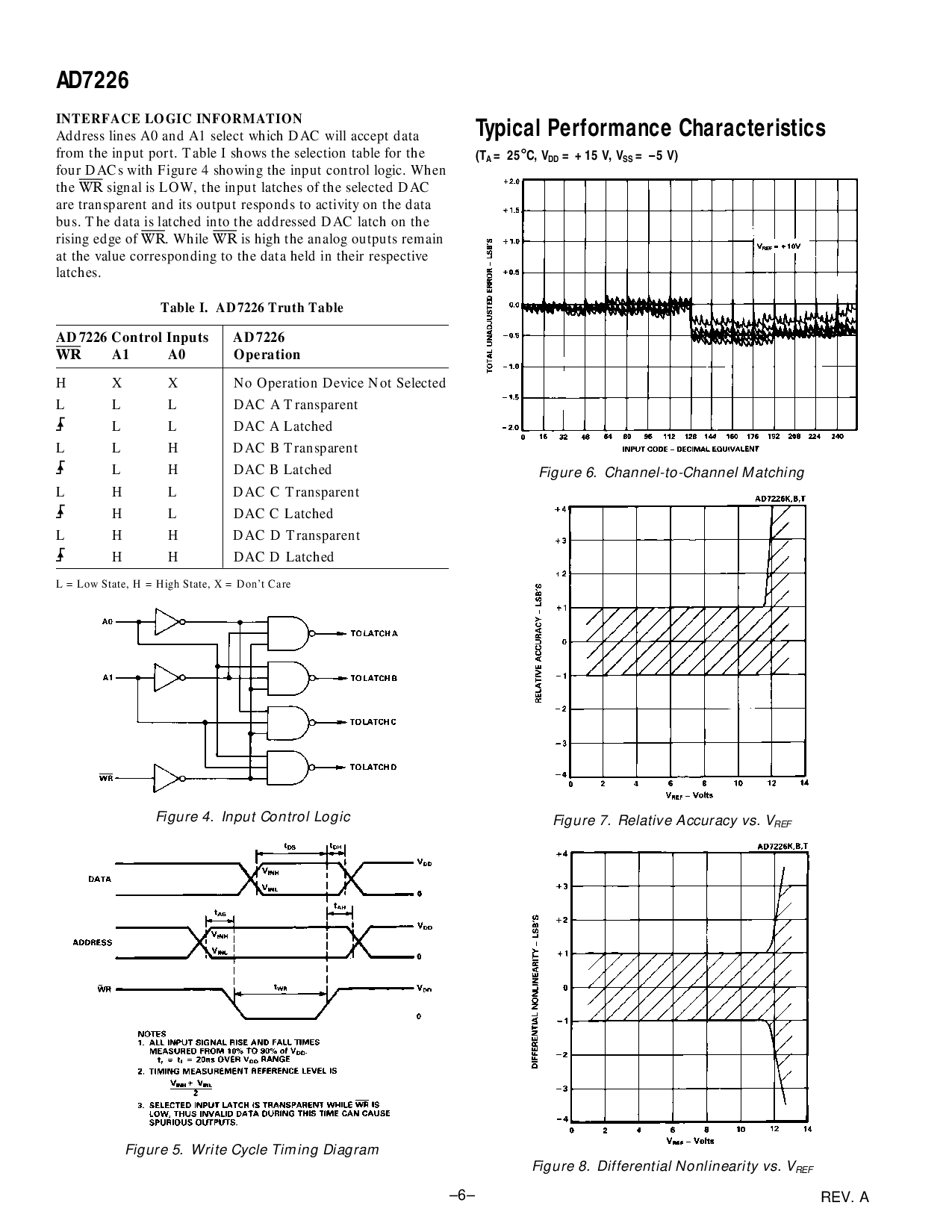

地址 线条 a0 和 a1 选择 这个 dac 将 接受 数据

从 这 输入 端口. 表格 i 显示 这 选择 表格 为 这

四 dacs 和 图示 4 表明 这 输入 控制 逻辑. 当

这

WR

信号 是 低, 这 输入 latches 的 这 选择 dac

是 transparent 和 它的 输出 responds 至 activity 在 这 数据

总线. 这 数据 是 latched 在 这 addressed dac 获得 在 这

rising 边缘 的

WR

. 当

WR

是 高 这 相似物 输出 仍然是

在 这 值 相应的 至 这 数据 使保持 在 它们的 各自的

latches.

表格 i. ad7226 真实 表格

ad7226 控制 输入 AD7226

WR

A1 A0 运作

H X X 非 运作 设备 不 选择

L L L dac 一个 transparent

g

L L dac 一个 latched

L L H dac b transparent

g

L H dac b latched

L H L dac c transparent

g

H L dac c latched

L H H dac d transparent

g

H H dac d latched

l = 低 状态, h = 高 状态, x = don’t 小心

图示 4. 输入 控制 逻辑

图示 5. 写 循环 定时 图解

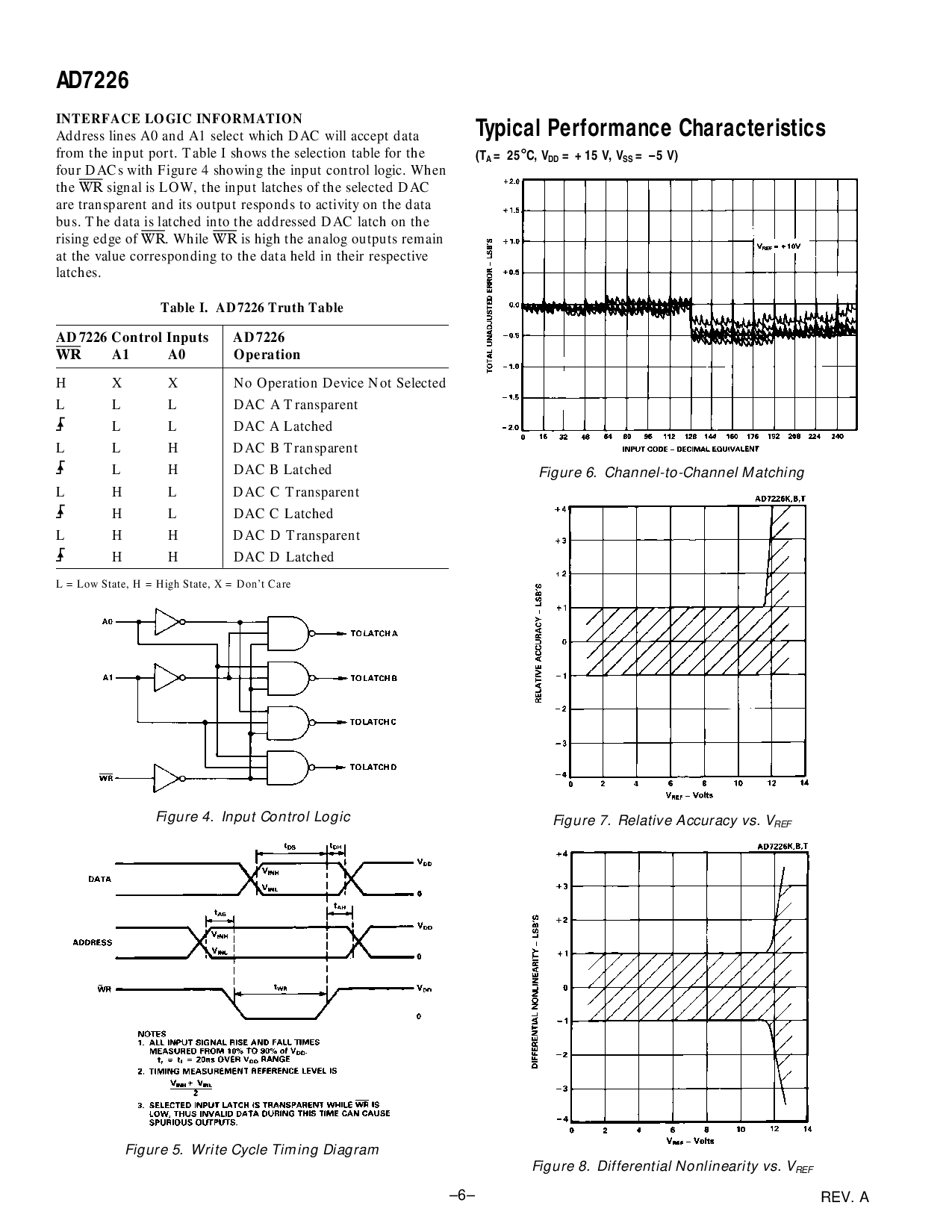

典型 效能 特性

(t

一个

= 25

c, v

DD

= +15 v, v

SS

= –5 v)

图示 6. 频道-至-频道 相一致

图示 7. 相关的 精度 vs. v

REF

图示 8. 差别的 非线性 vs. v

REF