100-mhz pentium

®

ii 时钟 synthesizer/驱动器 和

展开 spectrum 为 mobile 或者 desktop pcs

CY2280

Cypress 半导体 公司

•

3901 北 第一 街道

•

San Jose

•

ca 95134

•

408-943-2600

文档 #: 38-07207 rev. *a 修订 12月 08, 2002

0

特性

• mixed 2.5v 和 3.3v 运作

• 时钟 解决方案 为 pentium® ii, 和 其它 类似的 pro-

cessor-为基础 motherboards

— 四 2.5v cpu clocks 向上 至 100 mhz

— 第八 3.3v 同步. pci clocks, 一个 自由-运动

— 二 3.3v 48-mhz usb clocks

— 三 3.3v ref. clocks 在 14.318 mhz

— 二 2.5v apic clocks 在 14.318 mhz 或者 pci/2

• emi 控制

— 展开 spectrum clocking

— 工厂-非易失存储器 可编程序的 展开 spectrum

余裕

—

工厂-非易失存储器 可编程序的 输出 驱动 和

回转 比率

•

工厂-非易失存储器 可编程序的 cpu 时钟 发生率

为 custom 配置

•

有 在 空间-节省 48-管脚 ssop 包装

函数的 描述

这 cy2280 是 一个 展开 spectrum 时钟 synthesizer/驱动器 为

一个 pentium ii, 或者 其它 类似的 处理器-为基础 pc 需要

100-mhz 支持. 所有 的 这 必需的 系统 clocks 是 provid-

ed 在 一个 空间-节省 48-管脚 ssop 包装. 这 cy2280 能

是 使用 和 这 cy231x 为 一个 总的 解决方案 为 系统 和

sdram.

这 cy2280 提供 这 选项 的 展开 spectrum clocking

在 这 cpu 和 pci clocks 为 减少 emi. 一个 downspread

percentage 是 introduced 当 这 sel_ss

输入 是 asserted.

这 设备 能 是 run 没有 展开 spectrum 当 这

sel_ss

输入 是 deasserted. 这 percentage 的 spreading 是

非易失存储器-可编程序的 至 优化 emi-减少.

这 cy2280 有 电源-向下, cpu 停止, 和 pci 停止 管脚

为 电源 管理 控制. 这 信号 是 同步

在-碎片, 和 确保 glitch-自由 transitions 在 这 输出.

当 这 cpu_停止

输入 是 asserted, 这 cpu 时钟 输出-

puts 是 驱动 低. 当 这 pci_停止

输入 是 asserted,

这 pci 时钟 输出 (除了 这 自由-运动 pci 时钟) 是

驱动 低. 当 这 pwr_dwn

管脚 是 asserted, 这 谈及-

ence 振荡器 和 plls 是 shut 向下, 和 所有 输出 是

驱动 低.

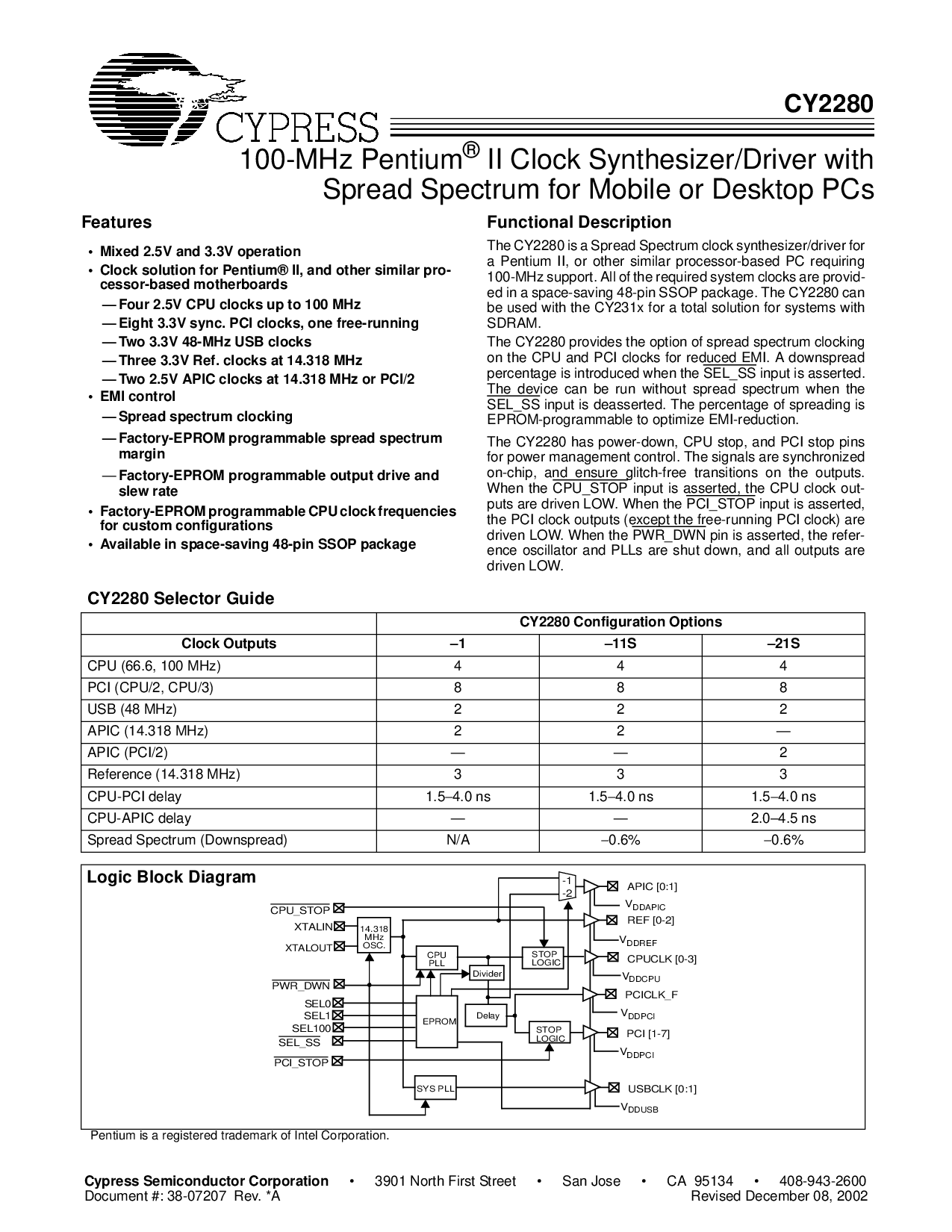

cy2280 选择 手册

cy2280 配置 选项

时钟 输出

–

1

–

11S

–

21S

cpu (66.6, 100 mhz) 4 4 4

pci (cpu/2, cpu/3) 8 8 8

usb (48 mhz) 2 2 2

apic (14.318 mhz) 2 2

—

apic (pci/2)

——

2

涉及 (14.318 mhz) 3 3 3

cpu-pci 延迟 1.5

−

4.0 ns 1.5

−

4.0 ns 1.5

−

4.0 ns

cpu-apic 延迟

——

2.0

–

4.5 ns

展开 spectrum (downspread) n/一个

−

0.6%

−

0.6%

pentium 是 一个 注册 商标 的 intel 公司.

逻辑 块 图解

非易失存储器

XTALOUT

XTALIN

apic [0:1]

14.318

MHz

osc.

SEL0

V

DDAPIC

CPU

PLL

SEL100

延迟

ref [0-2]

cpuclk [0-3]

V

DDCPU

pci [1-7]

pciclk_f

停止

停止

逻辑

逻辑

SEL1

usbclk [0:1]

sys pll

cpu_停止

pwr_dwn

分隔物

pci_停止

V

DDPCI

V

DDPCI

V

DDREF

V

DDUSB

-1

-2

sel_ss