高-精度 非易失存储器 可编程序的

单独的-pll 时钟 发生器

CY2077

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

文档 #: 38-07210 rev. *b 修订 12月 07, 2002

特性 益处

• 高-精度 pll 和 12-位 乘法器 和 10-位

分隔物

使能 综合 的 高级地 精确 和 稳固的 输出 时钟

发生率 和 零 ppm

• 非易失存储器-programmability

使能 快 turnaround 的 custom 发生率

• 3.3v 或者 5v 运作

支持 工业 标准 设计 platforms

• 运行 频率

— 390 khz–133 mhz 在 5v

— 390 khz–100 mhz 在 3.3v

维护 大多数 pc, networking, 和 消费者 产品

• 涉及 输入 从 也 一个 10–30 mhz 基本的

toned 结晶 或者 一个 1–75 mhz 外部 时钟

lowers 费用 的 振荡器 作 pll 能 是 编写程序 至 一个 高

频率 使用 也 一个 低-频率, 低-费用 结晶, 或者 一个

存在 系统 时钟

• 非易失存储器-可选择的 ttl 或者 cmos 职责-循环 水平

职责 循环 集中 在 1.5v 或者 v

DD

/2

提供 flexibility 至 维护 大多数 ttl 或者 cmos 产品

• 十六 可选择的 邮递-分隔 选项, 使用 也 pll

或者 涉及 振荡器/外部 时钟

提供 flexibility 在 输出 配置 和 测试

• 可编程序的 pwr_dwn 或者 oe 管脚, 和

异步的 或者 同步的 模式

使能 低-电源 运作 或者 输出 使能 函数 和

flexibility 为 系统 产品, 通过 可选择的 instanta-

neous 或者 同步的 改变 在 输出

• 低 jitter 输出 典型地

— 80 ps 在 3.3v/5v

合适的 为 大多数 pc, 消费者, 和 networking 产品

• 控制 上升 和 下降 时间 和 输出 回转 比率

有 更小的 emi 比 oscillators

• 有 在 两个都 商业的 和 工业的

温度 范围

合适的 至 合适 大多数 产品

• 工厂-可编程序的 设备 选项

容易 customization 和 快 turnaround

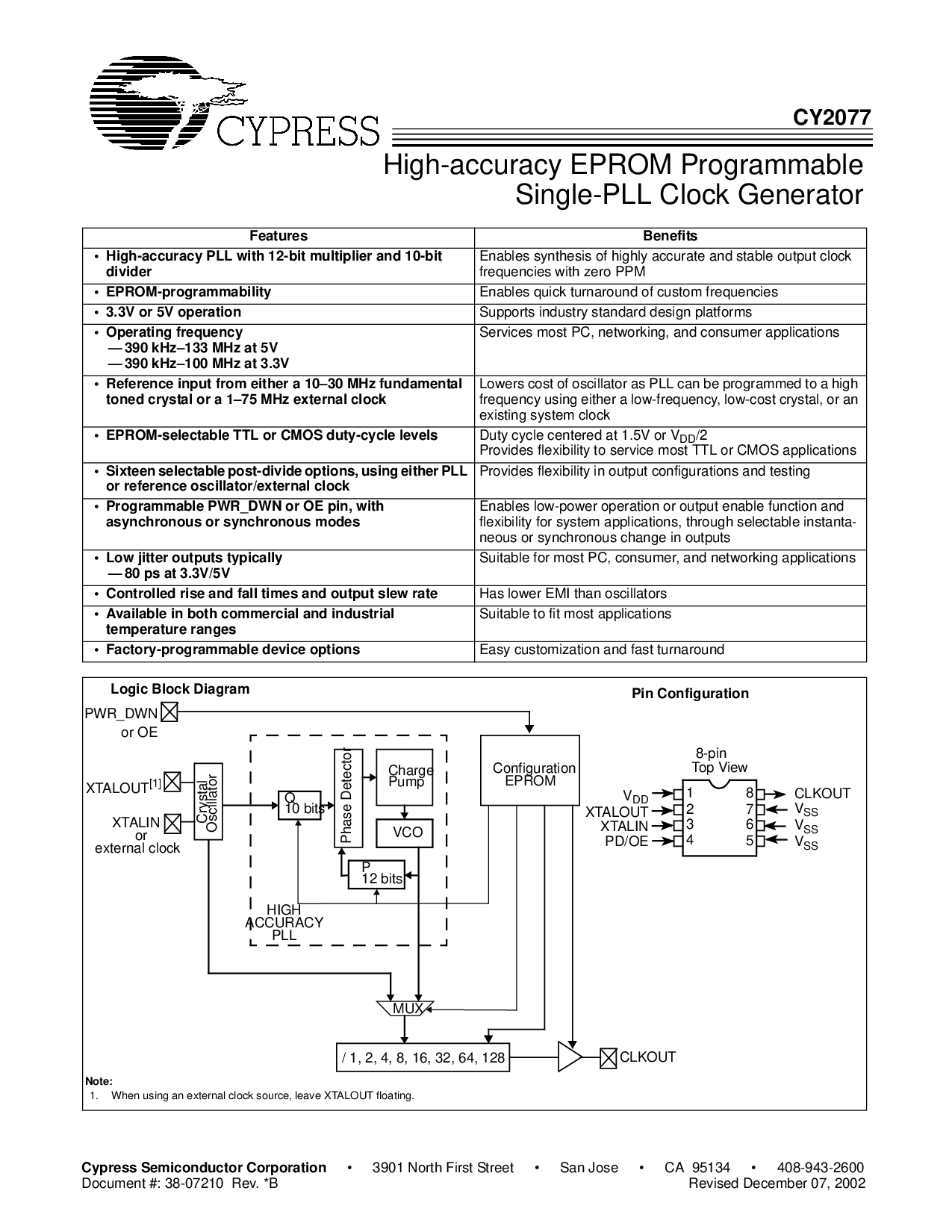

振荡器

逻辑 块 图解

XTALIN

pwr_dwn

配置

结晶

CLKOUT

/ 1, 2, 4, 8, 16, 32, 64, 128

或者 oe

MUX

高

精度

PLL

非易失存储器

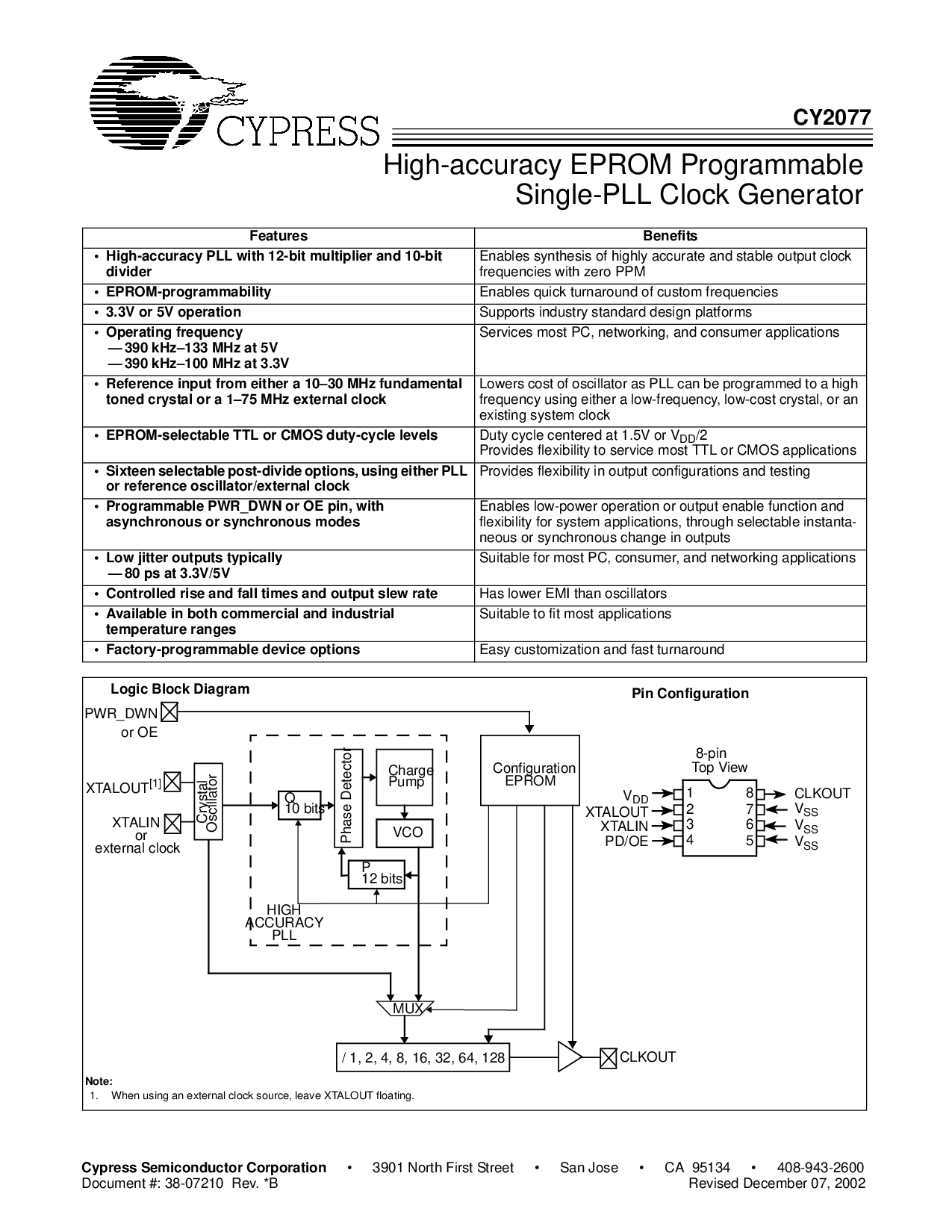

1

2

3

4

5

8

7

6

V

DD

XTALOUT

XTALIN

pd/oe

V

SS

CLKOUT

V

SS

V

SS

8-管脚

顶 视图

Q

10 位

P

12 位

阶段 探测器

承担

打气

VCO

或者

外部 时钟

管脚 配置

便条:

1. 当 使用 一个 外部 时钟 源, leave xtalout floating.

XTALOUT

[1]