初步的 技术的 数据 ad5601/ad5611/ad5621

rev. prc | 页 7 的 20

管脚 配置 和 function 描述

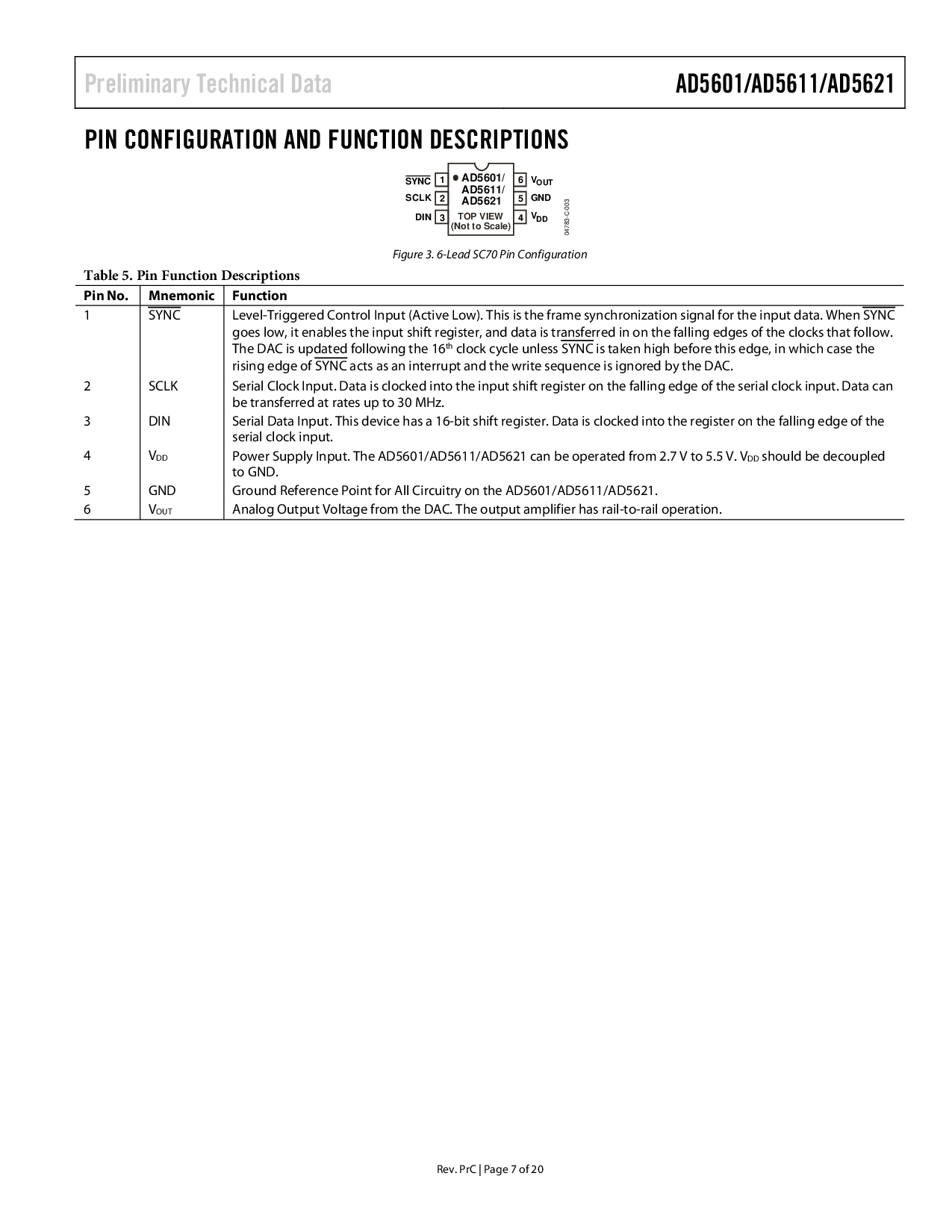

顶 视图

(不 至 规模)

V

DD

地

SCLK

DIN

ad5601/

ad5611/

AD5621

V

输出

同步

1

2

3

6

5

4

04783-c-003

图示 3. 6-含铅的 sc70 管脚 配置

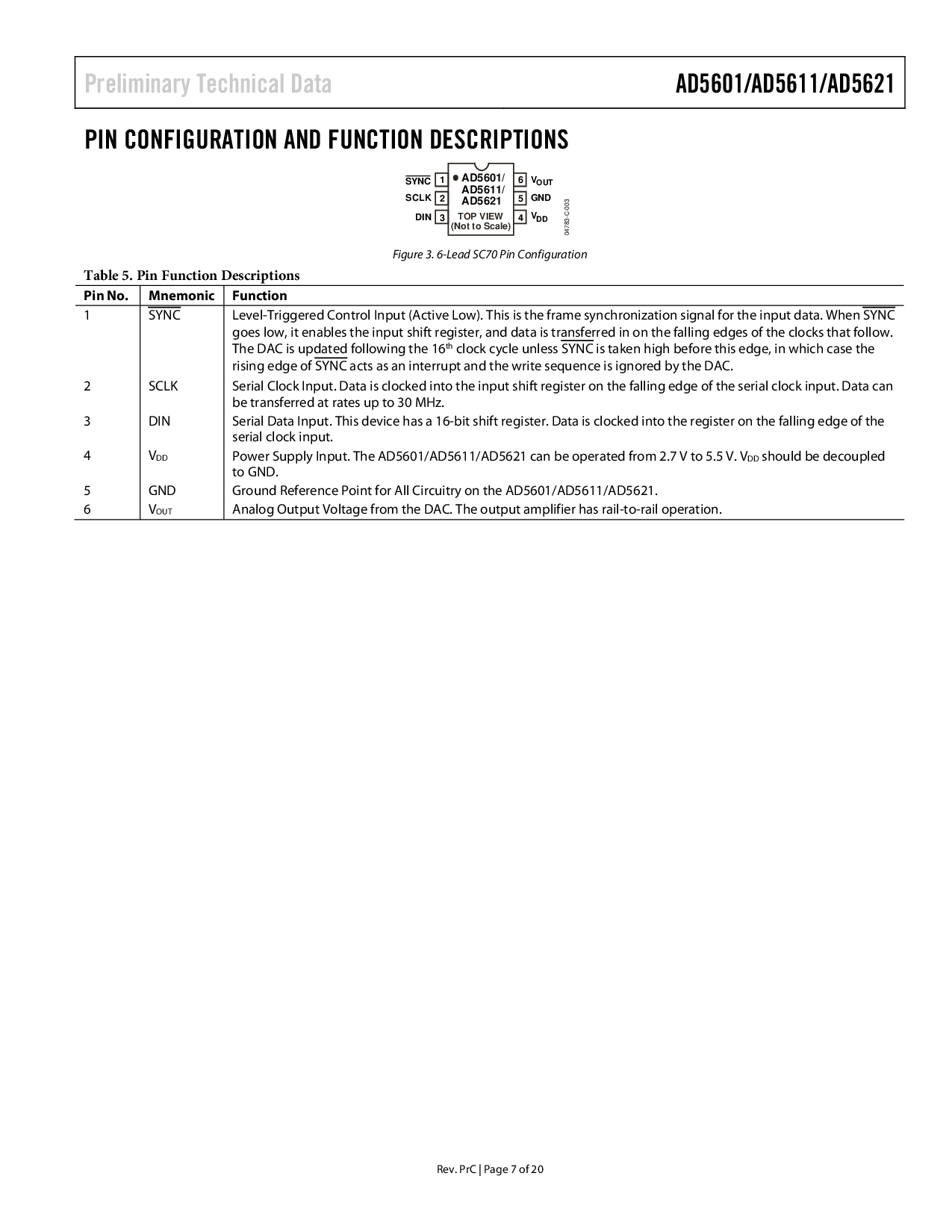

表格 5. 管脚 函数 描述

管脚 非. Mnemonic 函数

1

同步 水平的-triggered 控制 输入 (起作用的 low). 这个 是 这 框架 synchronization 信号 为 这 输入 数据. 当同步

变得 低, 它 使能 这 输入 变换 寄存器, 和 数据 是 transferred 在 在 这 下落 边缘s 的 这 clocks 那 follow.

这 dac 是 updated 下列的 这 16

th

时钟 循环 除非同步是 带去 高 在之前 这个边缘, 在 这个 情况 这

rising 边缘 的

同步acts 作 一个 中断 和 这 写 sequence 是 ignored 用 这 dac.

2 sclk

串行 时钟 输入. 数据 是 clocked 在 这 输入 变换 寄存器 在 这 falling 边缘 的 这 串行 时钟 输入. 数据 能

是 transferred 在 比率 向上 至 30 mhz.

3 din

串行 数据 输入. 这个 设备 有 一个 16-位 变换 寄存器. data 是 clocked 在 这 寄存器在 这 下落 边缘 的 这

串行 时钟 输入.

4 v

DD

电源 供应 输入. 这 ad5601/ad5611/ad5621 能 是 运作 从 2.7 v 至 5.5 v. v

DD

应当 是 decoupled

至 地.

5 地 地面 涉及 要点 为 所有电路系统 在 这 ad5601/ad5611/ad5621.

6 v

输出

相似物 输出 电压 从 这 dac. 这 output 放大器 有 栏杆-至-栏杆 运作.