应用 Hints

(持续)

14 left-justified 数据 Format

它 是 重要的 至 realize 那 这 输入 寄存器 的 这些

DACs 是 arranged 至 接受 一个 left-justified 数据 文字 从

这 微处理器 和 这 大多数 重大的 8 位 coming

第一 (字节 1) 和 这 更小的 4 位 second Left justification

simply 意思 那 这 二进制的 要点 是 assumed 至 是 located

至 这 left 的 这 大多数 重大的 bit

图示 3

显示 如何 这

12 位 的 DAC 数据 应当 是 arranged 在 2 8-位 寄存器

的 一个 8-位 处理器 在之前 正在 写 至 这 DAC

tlh5690-10

X

e

don’t 小心

图示 3 left-justified 数据 Format

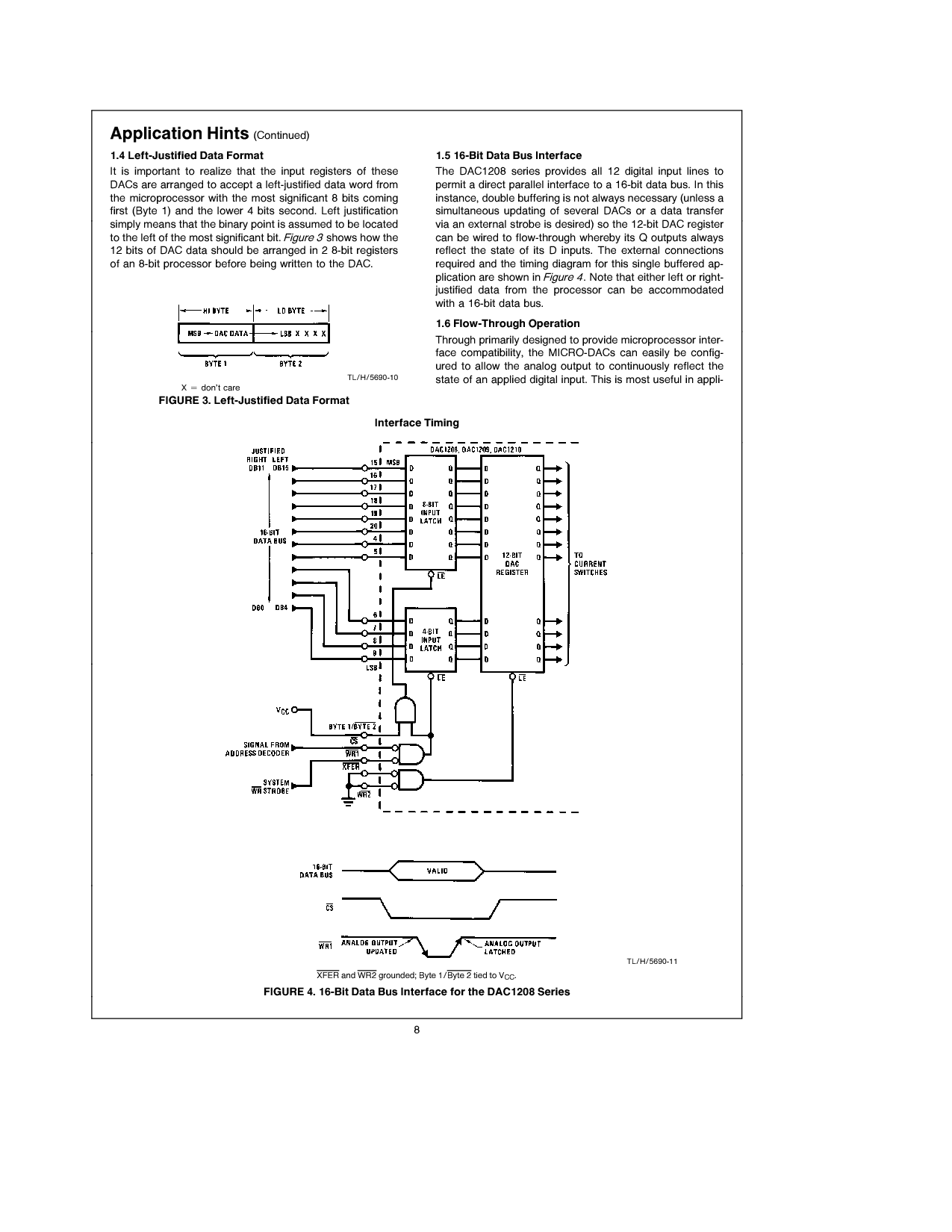

15 16-位 数据 总线 接口

这 DAC1208 序列 提供 所有 12 数字的 输入 线条 至

准许 一个 直接 并行的 接口 至 一个 16-位 数据 bus 在 这个

instance 翻倍 buffering 是 不 总是 需要 (除非 一个

同时发生的 updating 的 一些 DACs 或者 一个 数据 转移

通过 一个 外部 strobe 是 desired) 所以 这 12-位 DAC 寄存器

能 是 连线的 至 流动-通过 凭此 它的 Q 输出 总是

反映 这 状态 的 它的 D inputs 这 外部 连接

必需的 和 这 定时 图解 为 这个 单独的 缓冲 ap-

plication 是 显示 在

图示 4

便条 那 也 left 或者 正确的-

justified 数据 从 这 处理器 能 是 accommodated

和 一个 16-位 数据 bus

16 流动-通过 运作

通过 primarily 设计 至 提供 微处理器 inter-

面向 compatibility 这 微观的-dacs 能 容易地 是 config-

ured 至 准许 这 相似物 输出 至 continuously 反映 这

状态 的 一个 应用 数字的 input 这个 是 大多数 有用的 在 appli-

接口 定时

tlh5690-11

XFER 和 WR2 grounded 字节 1Byte 2 系 至 V

CC

图示 4 16-位 数据 总线 接口 为 这 DAC1208 序列

8