ds90c387a/ds90cf388a

双 Pixel LVDS 显示 接口 / fpd-link

一般 描述

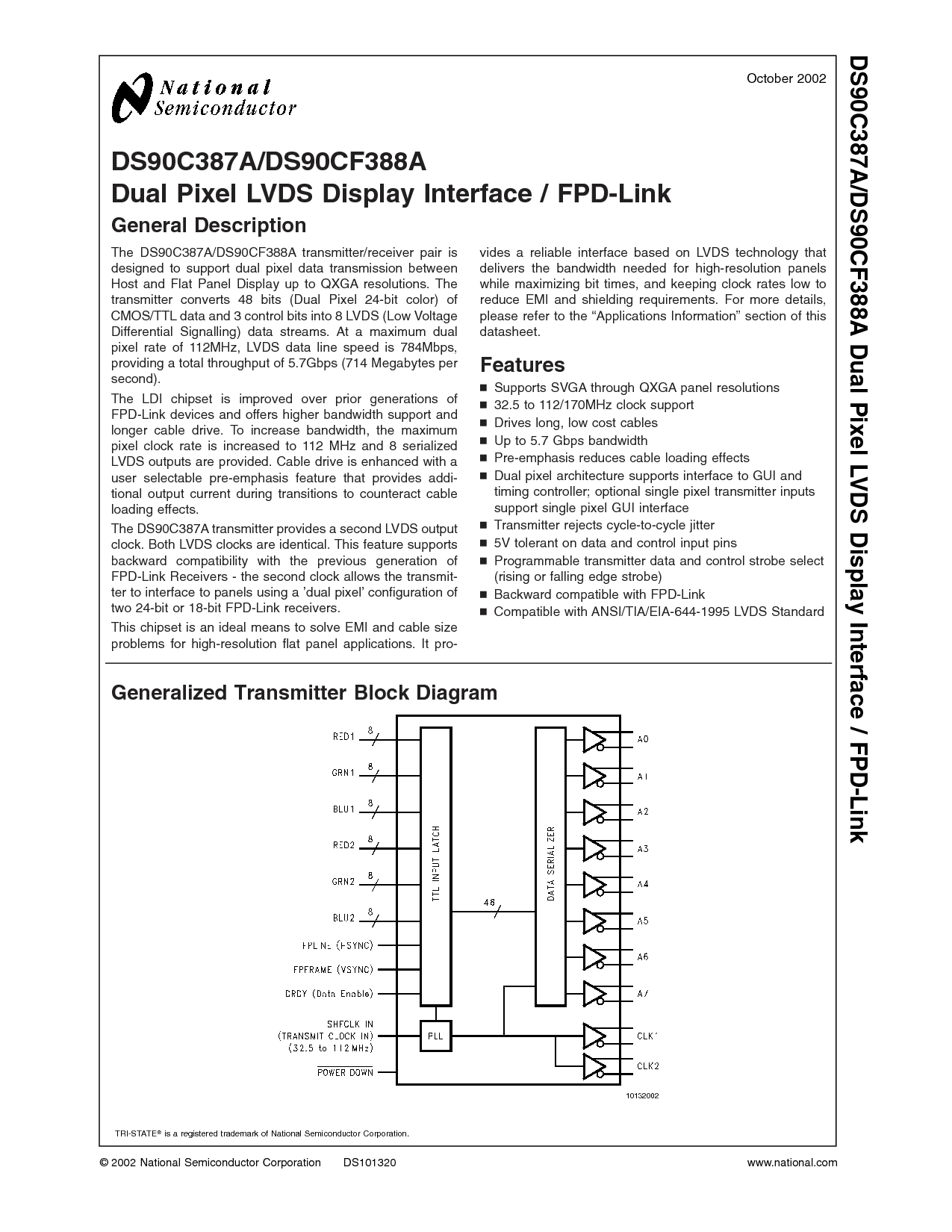

这 ds90c387a/ds90cf388a 传输者/接受者 一双 是

设计 至 支持 双 pixel 数据 传递 在

Host 和 Flat 嵌板 显示 向上 至 QXGA resolutions. 这

传输者 converts 48 位 (双 Pixel 24-位 颜色) 的

cmos/ttl 数据 和 3 控制 位 在 8 LVDS (低 电压

差别的 signalling) 数据 streams. 在 一个 最大 双

pixel 比率 的 112mhz, LVDS 数据 线条 速 是 784mbps,

供应 一个 总的 throughput 的 5.7gbps (714 Megabytes 每

第二).

这 LDI chipset 是 改进 在 较早的 generations 的

fpd-link 设备 和 提供 高等级的 带宽 支持 和

变长 缆索 驱动. 至 增加 带宽, 这 最大

pixel 时钟 比率 是 增加 至 112 MHz 和 8 serialized

LVDS 输出 是 提供. 缆索 驱动 是 增强 和 一个

用户 可选择的 前-emphasis 特性 那 提供 addi-

tional 输出 电流 在 transitions 至 counteract 缆索

加载 影响.

这 DS90C387A 传输者 提供 一个 第二 LVDS 输出

时钟. 两个都 LVDS clocks 是 完全同样的. 这个 特性 支持

backward 兼容性 和 这 previous 一代 的

fpd-link 接受者 - 这 第二 时钟 准许 这 transmit-

ter 至 接口 至 嵌板 使用 一个 ’dual pixel’ 配置 的

二 24-位 或者 18-位 fpd-link 接受者.

这个 chipset 是 一个 完美的 意思 至 solve EMI 和 缆索 大小

问题 为 高-决议 flat 嵌板 产品. 它 pro-

vides 一个 可依靠的 接口 为基础 在 LVDS 技术 那

delivers 这 带宽 需要 为 高-决议 嵌板

当 maximizing 位 时间, 和 keeping 时钟 比率 低 至

减少 EMI 和 防护 (所需的)东西. 为 更多 详细信息,

请 谈及 至 这 “Applications Information” 部分 的 这个

数据手册.

特性

n

支持 SVGA 通过 QXGA 嵌板 resolutions

n

32.5 至 112/170mhz 时钟 支持

n

驱动 长, 低 费用 cables

n

向上 至 5.7 Gbps 带宽

n

前-emphasis 减少 缆索 加载 影响

n

双 pixel architecture 支持 接口 至 GUI 和

定时 控制; optional 单独的 pixel 传输者 输入

支持 单独的 pixel GUI 接口

n

传输者 rejects 循环-至-循环 jitter

n

5V tolerant 在 数据 和 控制 输入 管脚

n

可编程序的 传输者 数据 和 控制 strobe 选择

(rising 或者 下落 边缘 strobe)

n

Backward 兼容 和 fpd-link

n

兼容 和 ansi/tia/eia-644-1995 LVDS 标准

Generalized 传输者 块 图解

10132002

触发-状态

®

是 一个 注册 商标 的 国家的 半导体 公司.

October 2002

ds90c387a/ds90cf388a 双 Pixel LVDS 显示 接口 / fpd-link

© 2002 国家的 半导体 公司 DS101320 www.国家的.com