8

hm6264a 序列 hm6264a 序列

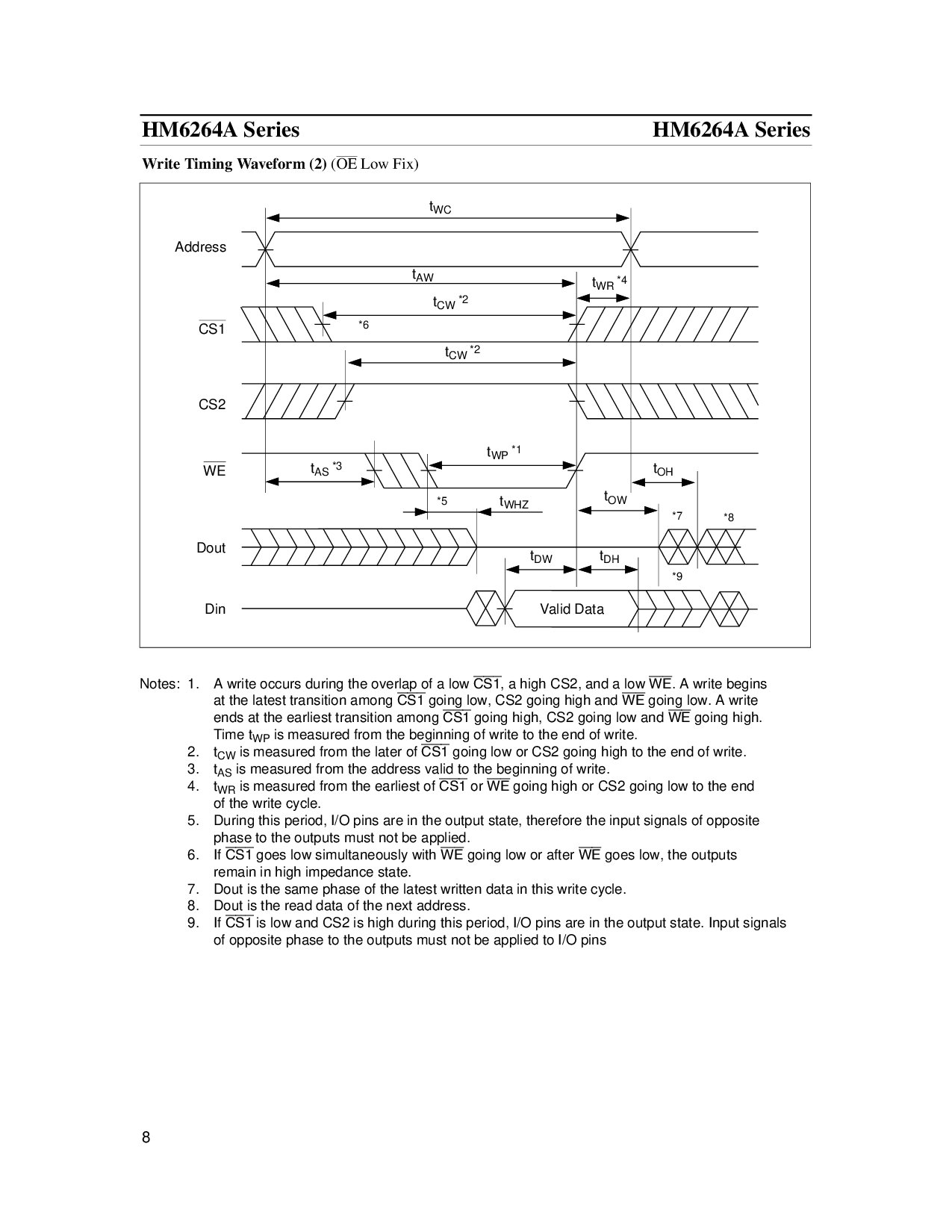

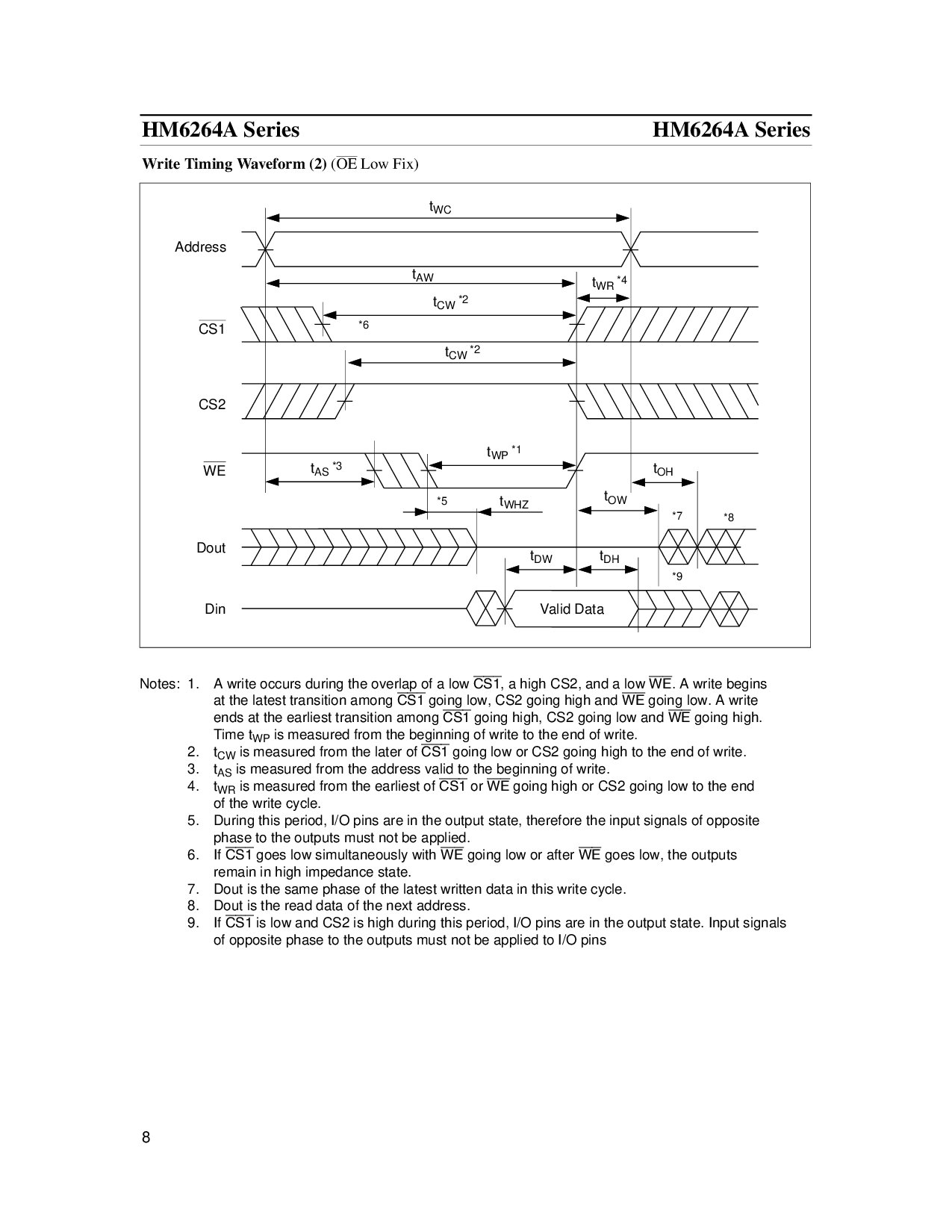

写 定时 波形 (2)

(

OE

低 fix)

t

WC

t

AW

t

CW

*2

*6

t

CW

*2

t

WP

*1

t

作

*3

*5

t

WHZ

t

OH

t

OW

*7

*8

t

DH

t

DW

*9

Address

CS1

CS2

Dout

Din

WE

t

WR

*4

有效的 data

注释: 1.

2.

3.

4.

5.

6.

7.

8.

9.

一个 写 occurs 在 这 overlap 的 一个 低

CS1

, 一个 高 cs2, 和 一个 低

我们

. 一个 写 begins

在 这 最新的 转变 among

CS1

going 低, cs2 going 高 和

我们

going 低. 一个 写

ends 在 这 earliest 转变 among

CS1

going 高, cs2 going 低 和

我们

going 高.

时间 t

WP

是 量过的 从 这 beginning 的 写 至 这 终止 的 写.

t

CW

是 量过的 从 这 后来的 的

CS1

going 低 或者 cs2 going 高 至 这 终止 的 写.

t

作

是 量过的 从 这 地址 有效的 至 这 beginning 的 写.

t

WR

是 量过的 从 这 earliest 的

CS1

或者

我们

going 高 或者 cs2 going 低 至 这 终止

的 这 写 循环.

在 这个 时期, i/o 管脚 是 在 这 输出 状态, 因此 这 输入 信号 的 opposite

阶段 至 这 输出 必须 不 是 应用.

如果

CS1

变得 低 同时发生地 和

我们

going 低 或者 之后

我们

变得 低, 这 输出

仍然是 在 高 阻抗 状态.

dout 是 这 一样 阶段 的 这 最新的 写 数据 在 这个 写 循环.

dout 是 这 读 数据 的 这 next 地址.

如果

CS1

是 低 和 cs2 是 高 在 这个 时期, i/o 管脚 是 在 这 输出 状态. 输入 信号

的 opposite 阶段 至 这 输出 必须 不 是 应用 至 i/o pins