cmos sramk6t1008c2e 家族

修订 3.0

march 2000

8

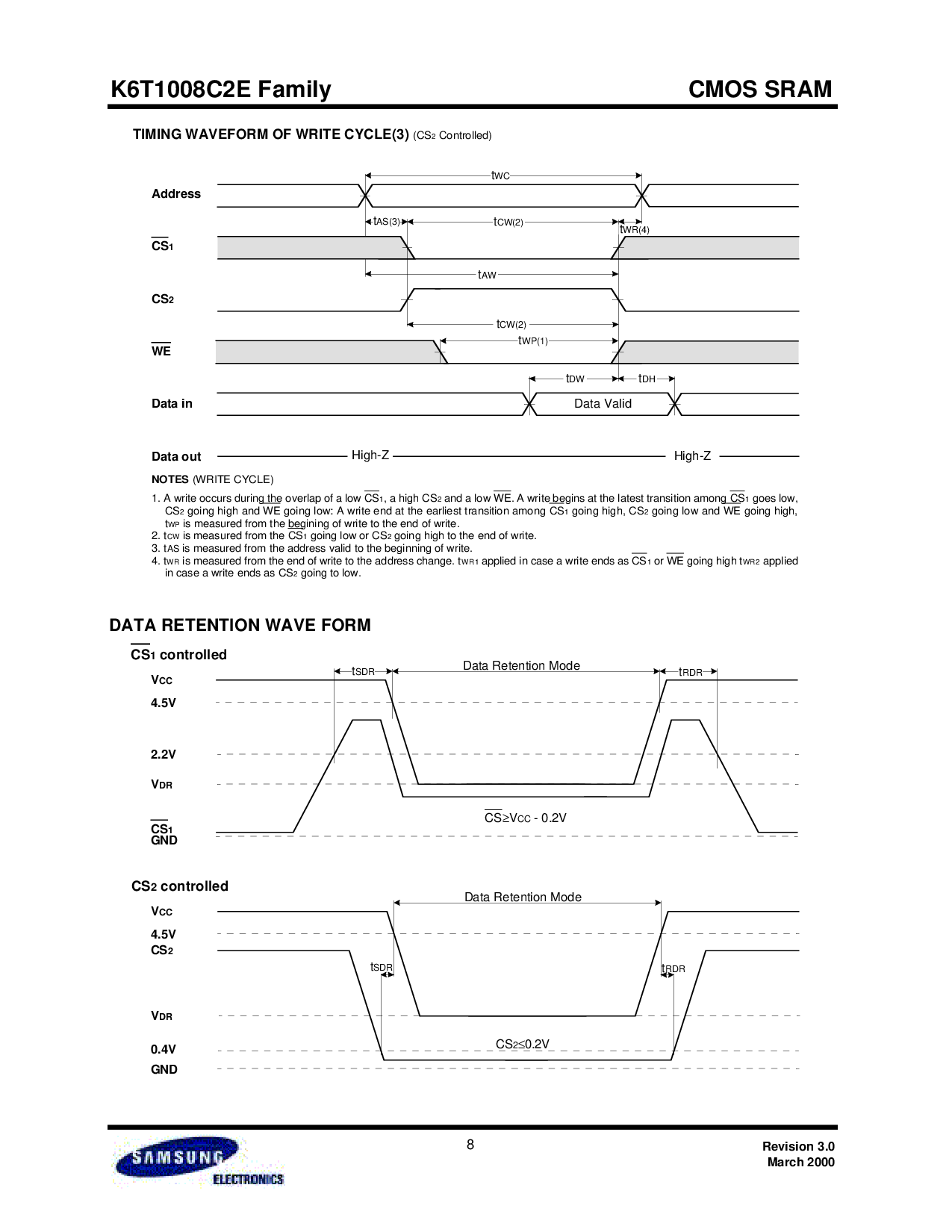

数据 保持 波 表格

CS1控制

VCC

4.5v

2.2v

VDR

CS1

地

数据 保持 模式

CS

≥

VCC- 0.2v

tSDR

tRDR

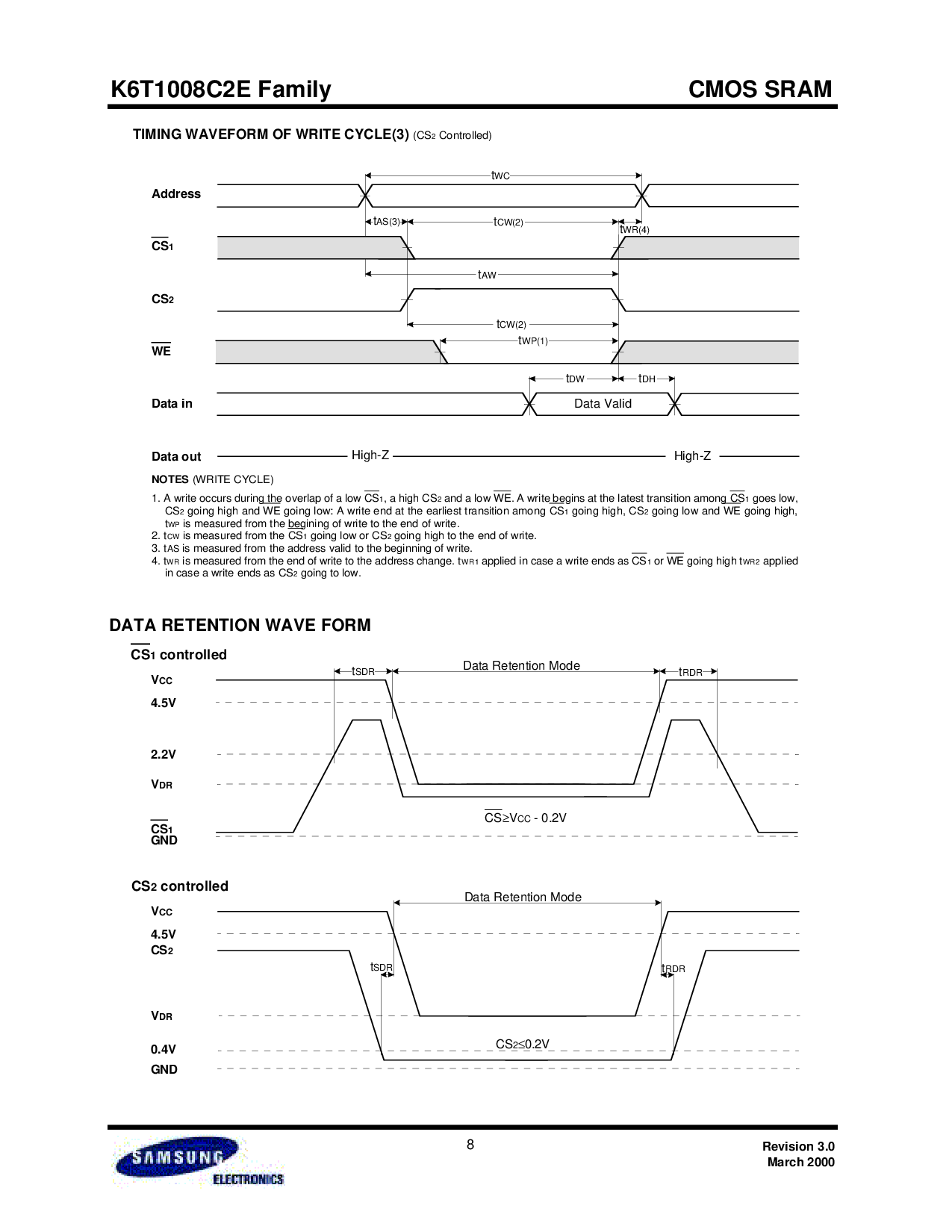

定时 波形 的 写 循环(3)

(cs2控制)

地址

CS1

tAW

注释

(写 循环)

1. 一个 写 occurs 在 这 overlap 的 一个 低CS1, 一个 高 cs2和 一个 低我们. 一个 写 begins 在 这 最新的 转变 amongCS1变得 低,

CS2going 高 和我们going 低: 一个 写 终止 在 这 earliest 转变 amongCS1going 高, cs2going 低 和我们going 高,

tWP是 量过的 从 这 begining 的 写 至 这 终止 的 写.

2. tCW是 量过的 从 这CS1going 低 或者 cs2going 高 至 这 终止 的 写.

3. t作是 量过的 从 这 地址 有效的 至 这 beginning 的 写.

4. tWR是 量过的 从 这 终止 的 写 至 这 地址 改变. tWR1应用 在 情况 一个 写 ends 作CS1或者我们going 高 tWR2应用

在 情况 一个 写 ends 作 cs2going 至 低.

CS2

tcw(2)

我们

数据 在

数据 有效的

数据 输出

高-z

高-z

tcw(2)

twr(4)

twp(1)

tDW

tDH

t作(3)

tWC

CS2控制

VCC

4.5v

0.4v

VDR

CS2

地

数据 保持 模式

tSDR

tRDR

CS2

≤

0.2v