4

AT89C55WD

1921B

–

微观的

–

09/02

管脚 描述

VCC

供应 电压.

地

地面.

Port 0

端口 0 是 一个 8-位 打开 流 bi-directional i/o 端口. 作 一个 输出 端口, 各自 管脚 能 下沉 第八

TTL 输入. 当 1s 是 写 至 端口 0 管脚, 这 管脚 能 是 使用 作 高-阻抗

输入.

端口 0 能 也 是 配置 至 是 这 多路复用 低-顺序 地址/数据 总线 在

accesses 至 外部 程序 和 数据 记忆. 在 这个 模式, P0 有 内部的 拉-ups.

端口 0 也 receives 这 代号 字节 在 Flash 程序编制 和 输出 这 代号 字节

在 程序 verification.

外部 拉-ups 是 必需的 在 程序 verification.

Port 1

端口 1 是 一个 8-位 bi-directional i/o 端口 和 内部的 拉-ups. 这 端口 1 输出 缓存区 能

下沉/源 四 TTL 输入. 当 1s 是 写 至 端口 1 管脚, 它们 是 牵引的 高 用 这

内部的 拉-ups 和 能 是 使用 作 输入. 作 输入, 端口 1 管脚 那 是 externally 正在

牵引的 低 将 源 电流 (i

IL

) 因为 的 这 内部的 拉-ups.

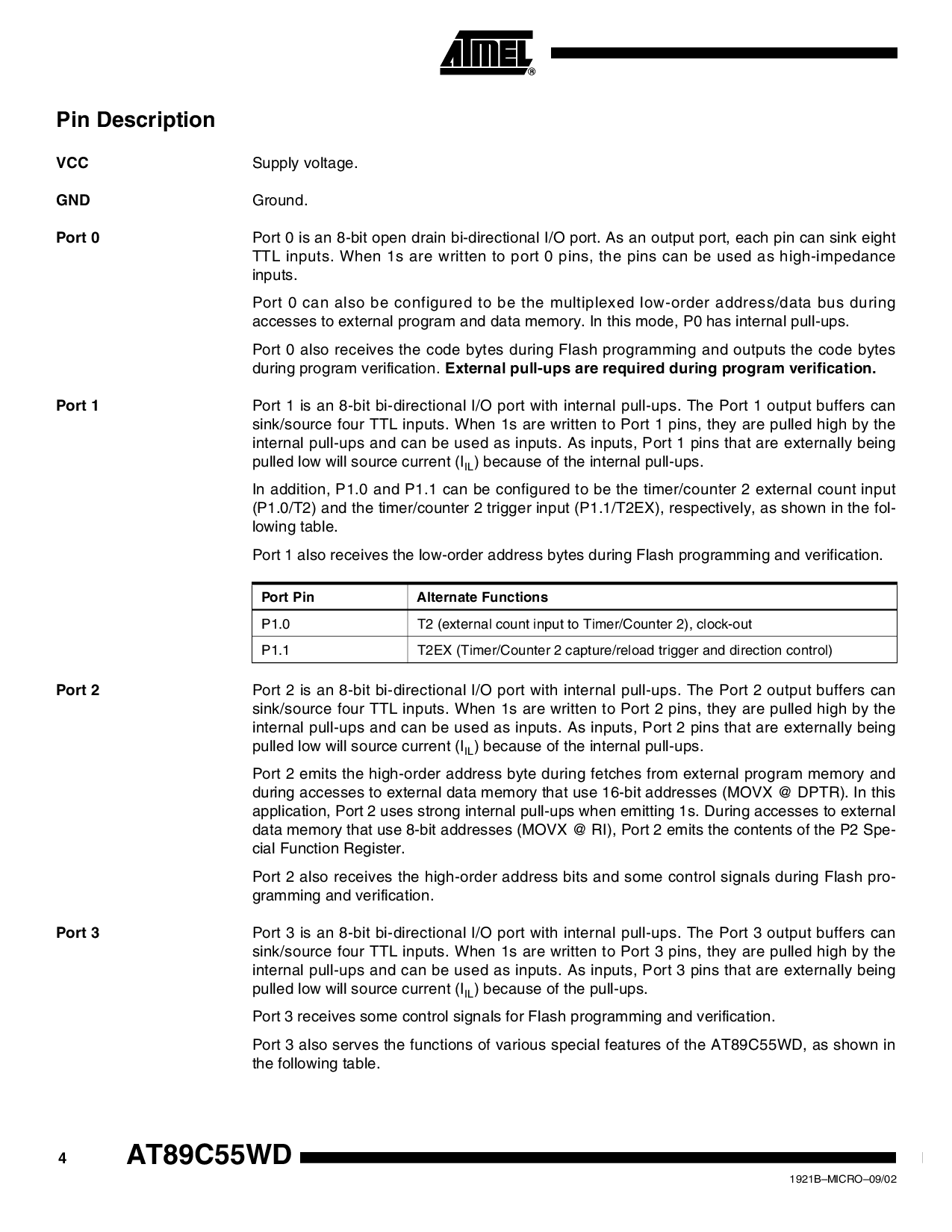

在 增加, p1.0 和 p1.1 能 是 配置 至 是 这 计时器/计数器 2 外部 计数 输入

(p1.0/t2) 和 这 计时器/计数器 2 触发 输入 (p1.1/t2ex), 各自, 作 显示 在 这 fol-

lowing 表格.

端口 1 也 receives 这 低-顺序 地址 字节 在 Flash 程序编制 和 verification.

Port 2

端口 2 是 一个 8-位 bi-directional i/o 端口 和 内部的 拉-ups. 这 端口 2 输出 缓存区 能

下沉/源 四 TTL 输入. 当 1s 是 写 至 端口 2 管脚, 它们 是 牵引的 高 用 这

内部的 拉-ups 和 能 是 使用 作 输入. 作 输入, 端口 2 管脚 那 是 externally 正在

牵引的 低 将 源 电流 (i

IL

) 因为 的 这 内部的 拉-ups.

端口 2 emits 这 高-顺序 地址 字节 在 fetches 从 外部 程序 记忆 和

在 accesses 至 外部 数据 记忆 那 使用 16-位 地址 (movx @ dptr). 在 这个

应用, 端口 2 使用 强 内部的 拉-ups 当 发出 1s. 在 accesses 至 外部

数据 记忆 那 使用 8-位 地址 (movx @ ri), 端口 2 emits 这 内容 的 这 P2 spe-

cial 函数 寄存器.

端口 2 也 receives 这 高-顺序 地址 位 和 一些 控制 信号 在 Flash pro-

gramming 和 verification.

Port 3

端口 3 是 一个 8-位 bi-directional i/o 端口 和 内部的 拉-ups. 这 端口 3 输出 缓存区 能

下沉/源 四 TTL 输入. 当 1s 是 写 至 端口 3 管脚, 它们 是 牵引的 高 用 这

内部的 拉-ups 和 能 是 使用 作 输入. 作 输入, 端口 3 管脚 那 是 externally 正在

牵引的 低 将 源 电流 (i

IL

) 因为 的 这 拉-ups.

端口 3 receives 一些 控制 信号 为 Flash 程序编制 和 verification.

端口 3 也 serves 这 功能 的 各种各样的 特定的 特性 的 这 at89c55wd, 作 显示 在

这 下列的 表格.

端口 管脚 Alternate 功能

p1.0 T2 (外部 计数 输入 至 计时器/计数器 2), 时钟-输出

p1.1 T2EX (计时器/计数器 2 俘获/再装填 触发 和 方向 控制)