六月 2003

1

© 2003 actel 公司

v3.1

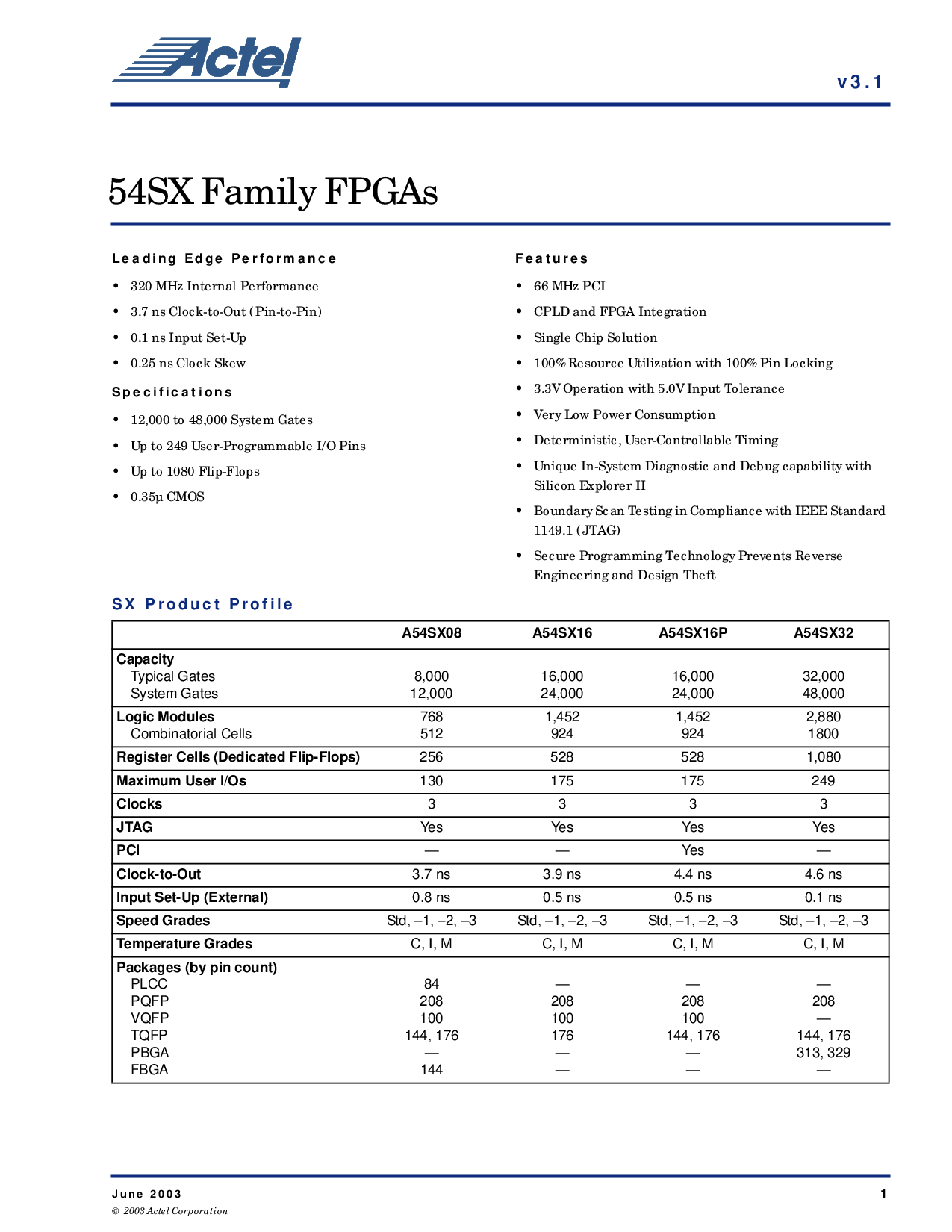

54sx 家族 fpgas

leading 边缘 效能

• 320 mhz 内部的 效能

• 3.7 ns 时钟-至-输出 (管脚-至-管脚)

• 0.1 ns 输入 设置-向上

• 0.25 ns 时钟 skew

规格

• 12,000 至 48,000 系统 门

• 向上 至 249 用户-可编程序的 i/o 管脚

• 向上 至 1080 flip-flops

• 0.35µ cmos

特性

• 66 mhz pci

• cpld 和 fpga integration

• 单独的 碎片 解决方案

• 100% resource utilization 和 100% 管脚 locking

• 3.3v 运作 和5.0v 输入 容忍

• 非常 低 电源 消耗量

• deterministic, 用户-controllable 定时

• 唯一的 在-系统 diagnostic 和 debug 能力 和

硅 explorer ii

• boundary scan 测试 在 竞赛liance 和 ieee 标准

1149.1 (jtag)

• secure 程序编制 技术 阻止 反转

engineering 和 设计 theft

sx 产品 profile

A54SX08 A54SX16 A54SX16P A54SX32

Capacity

Typical 门

系统 门

8,000

12,000

16,000

24,000

16,000

24,000

32,000

48,000

逻辑 modules

combinatorial cells

768

512

1,452

924

1,452

924

2,880

1800

寄存器 cells (dedicated flip-flops)

256 528 528 1,080

最大 用户 i/os

130 175 175 249

Clocks

3333

JTAG

YesYesYesYes

PCI

——Yes—

时钟-至-输出

3.7 ns 3.9 ns 4.4 ns 4.6 ns

输入 设置-向上 (外部)

0.8 ns 0.5 ns 0.5 ns 0.1 ns

速 grades

标准, –1, –2, –3 标准, –1, –2, –3 标准, –1, –2, –3 标准, –1, –2, –3

温度 grades

c, i, m c, i, m c, i, m c, i, m

包装 (用 管脚 计数)

PLCC

PQFP

VQFP

TQFP

PBGA

FBGA

84

208

100

144, 176

—

144

—

208

100

176

—

—

—

208

100

144, 176

—

—

—

208

—

144, 176

313, 329

—