x84161/641/129

3

设备 运作

这 x84161/641/129 是 串行 eeproms 设计 至

interface 直接地 和 大多数 微处理器 buses. stan-

dard ce, oe, 和 我们 信号 控制 这 读 和 写

行动, 和 一个 单独的 l/o 线条 是 使用 至 send 和

receive 数据 和 commands serially.

数据 定时

数据 输入 在 这 l/o 线条 是 latched 在 这 rising 边缘 的

也 我们

或者 ce, whichever occurs first. 数据 输出 在

这 l/o 线条 是 起作用的 whenever 两个都 oe 和 ce 是 低.

小心 应当 是 带去 至 确保 那 我们 和 oe 是

never 两个都 低 当 ce 是 低.

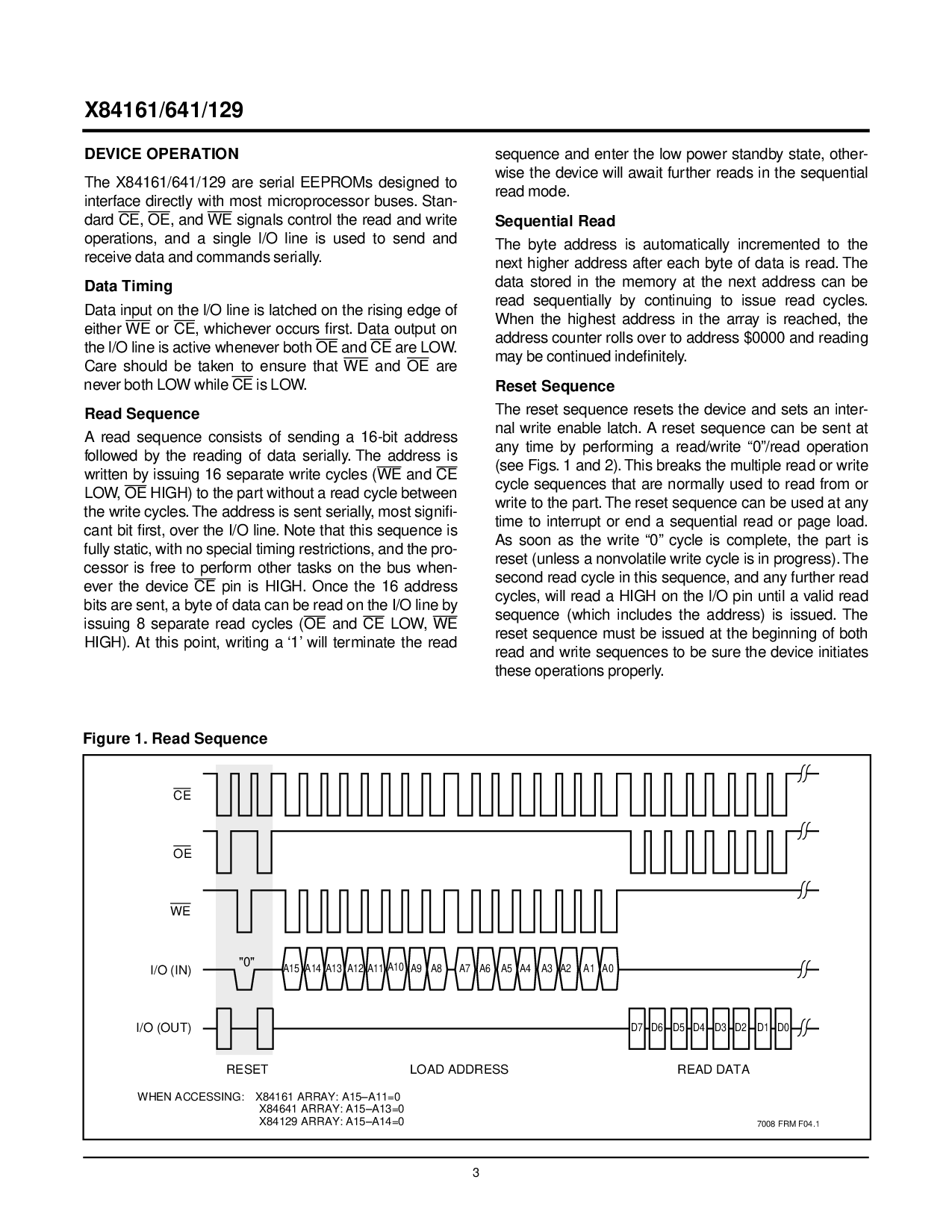

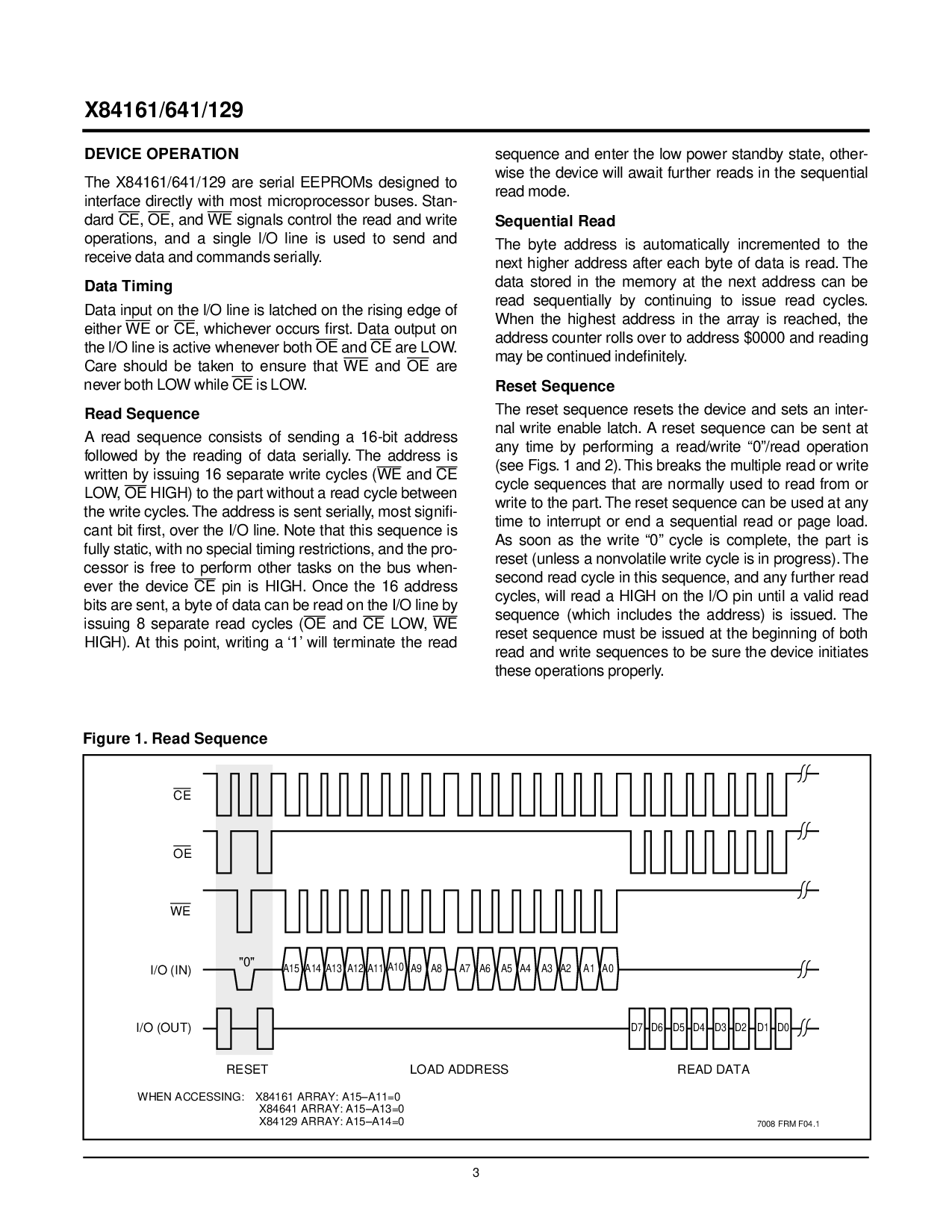

读 sequence

一个 读 sequence 组成 的 sending 一个 16-位 地址

followed 用 这 读 的 数据 serially. 这 地址 是

written 用 issuing 16 独立的 写 循环 (我们 和 ce

低, oe高) 至 这 部分 没有 一个 读 循环 在

这 写 循环. 这 地址 是 sent serially, 大多数 signifi-

cant 位 first, 在 这 i/o 线条. 便条 那 这个 sequence 是

全部地 静态的, 和 非 特定的 定时 restrictions, 和 这 pro-

cessor 是 自由 至 执行 其它 tasks 在 这 总线 当-

ever 这 设备 ce 管脚 是 高. once 这 16 地址

位 是 sent, 一个 字节 的 数据 能 是 读 在 这 i/o 线条 用

issuing 8 独立的 读 循环 (oe 和 ce 低, 我们

高).在 这个 要点, writing 一个 ‘1’ 将 terminate 这 读

sequence 和 enter 这 低 电源 备用物品 状态, 其它-

wise 这 设备 将 await 更远 读 在 这 sequential

读 模式.

sequential 读

这 字节 地址 是 automatically incremented 至 这

next 高等级的 地址 之后 各自 字节 的 数据 是 读. 这

数据 贮存 在 这 记忆 在 这 next 地址 能 是

读 sequentially 用 continuing 至 公布 读 循环.

当 这 最高的 地址 在 这 排列 是 reached, 这

地址 计数器 rolls 在 至 地址 $0000 和 读

毫安y 是 持续 indefinitely.

重置 sequence

这 重置 sequence resets 这 设备 和 sets 一个 inter-

nal 写 使能 获得. 一个 重置 sequence 能 是 sent 在

一个y 时间 用 performing 一个 读/写 “0”/读 运作

(看 figs. 1 和 2). 这个 breaks 这 多样的 读 或者 写

循环 sequences 那 是 正常情况下 使用 至 读 从 或者

write 至 这 部分. 这 重置 sequence 能 是 使用 在 任何

时间 至 中断 或者 终止 一个 sequential 读 或者 页 加载.

作 soon 作 这 写 “0” 循环 是 完全, 这 部分 是

重置 (除非 一个 nonvolatile 写 循环 是 在 progress). 这

第二 读 循环 在 这个 sequence, 和 任何 更远 读

循环, 将 读 一个 高 在 这 l/o 管脚 直到 一个 有效的 读

sequence (这个 包含 这 地址) 是 issued. 这

重置 sequence 必须 是 issued 在 这 beginning 的 两个都

读 和 写 sequences 至 是 确信 这 设备 initiates

这些 行动 合适的.

图示 1. 读 sequence

CE

OE

我们

i/o (在)

"0"

重置

当 accessing: x84161 排列: a15–a11=0

x84641 排列: a15–a13=0

x84129 排列: a15–a14=0

加载 地址 读 数据

A15 A14 A13 A12 A11

A10

A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

i/o (输出)

7008 frm f04.1

D7 D6 D5 D4 D3 D2 D1 D0