R

十一月 9, 1998 (版本 3.1) 7-9

xc3000 序列 地方 可编程序的 门 arrays

7

configurable 逻辑 块

这 排列 的 clbs 提供 这 函数的 elements 从

这个 这 用户’s 逻辑 是 构成. 这 逻辑 blocks 是

arranged 在 一个 矩阵变换 在里面 这 perimeter 的 iobs. 为

例子, 这 xc3020a 有 64 此类 blocks arranged 在 8

rows 和 8 columns. 这 开发 系统 是 使用 至

compile 这 配置 数据 这个 是 至 是 承载 在

这 内部的 配置 记忆 至 定义 这 运作

和 interconnection 的 各自 块. 用户 定义 的 clbs

和 它们的 interconnecting 网络 将 是 完毕 用 自动-

matic 转变 从 一个 图式-俘获 逻辑 图解 或者

optionally 用 installing 库 或者 用户 macros.

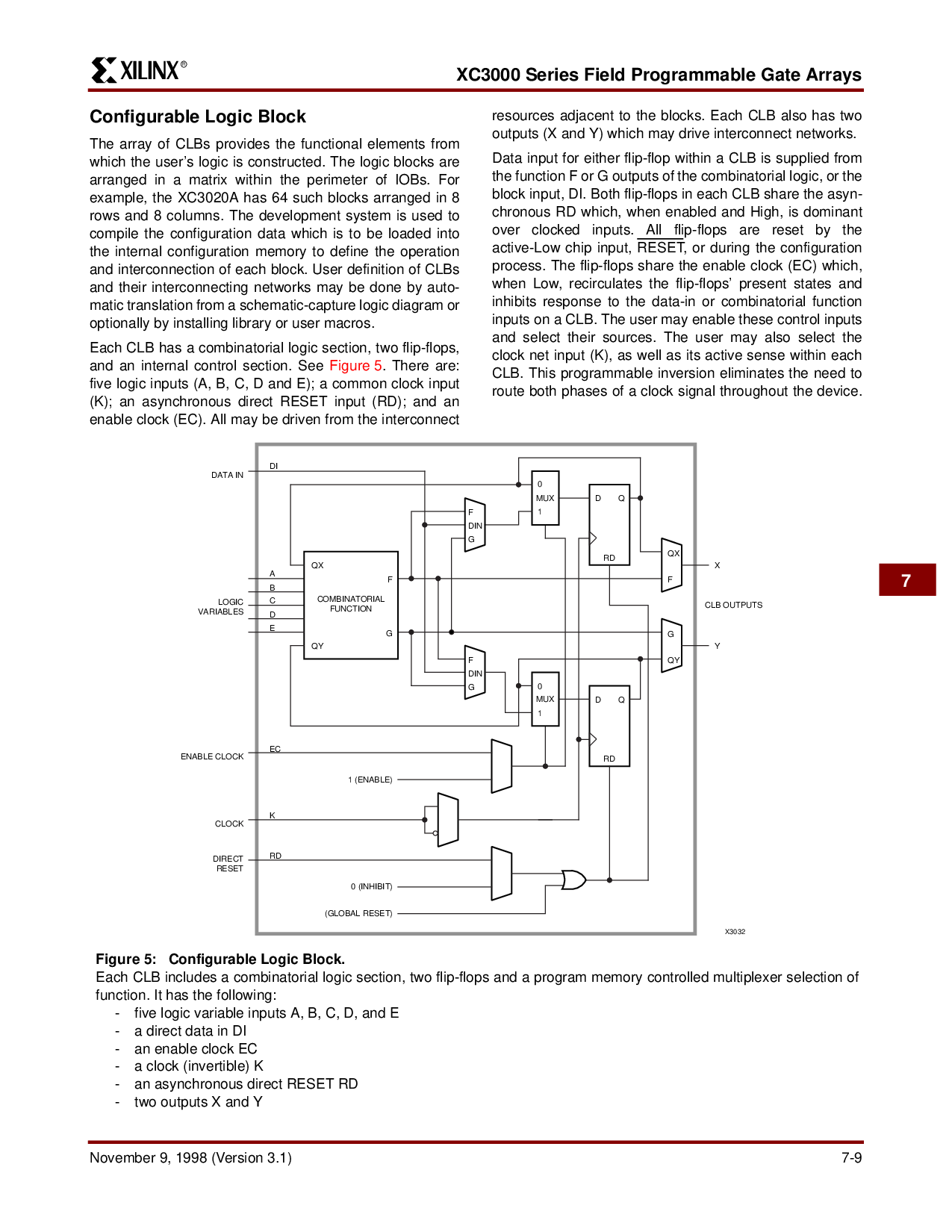

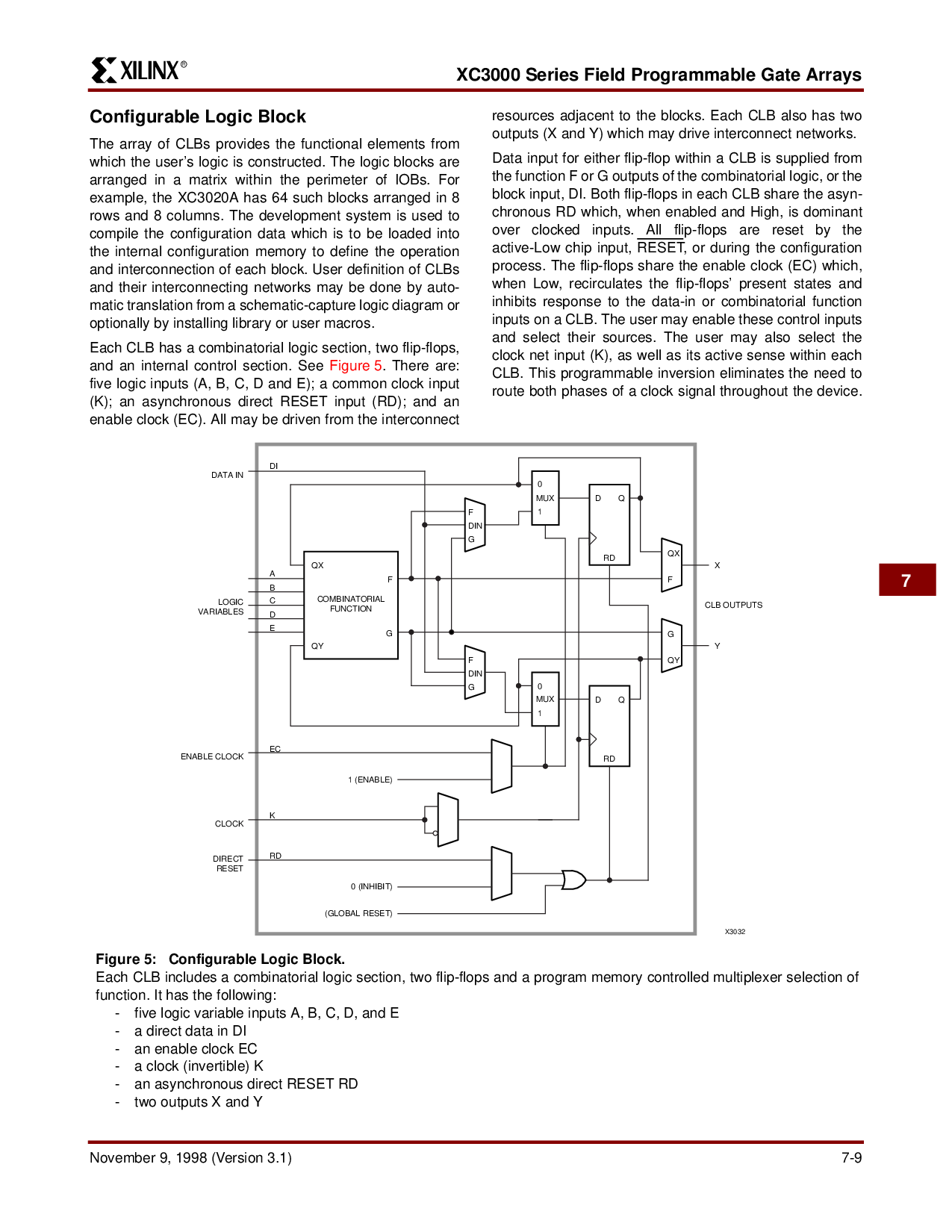

各自 clb 有 一个 combinatorial 逻辑 部分, 二 flip-flops,

和 一个 内部的 控制 部分. 看图示 5. 那里 是:

five 逻辑 输入 (一个, b, c, d 和 e); 一个 一般 时钟 输入

(k); 一个 异步的 直接 重置 输入 (rd); 和 一个

使能 时钟 (ec). 所有 将 是 驱动 从 这 interconnect

resources 调整 至 这 blocks. 各自 clb 也 有 二

输出 (x 和 y) 这个 将 驱动 interconnect 网络.

数据 输入 为 也 flip-flop 在里面 一个 clb 是 有提供的 从

这 函数 f 或者 g 输出 的 这 combinatorial 逻辑, 或者 这

块 输入, di. 两个都 flip-flops 在 各自 clb share 这 asyn-

chronous rd 这个, 当 使能 和 高, 是 首要的

在 clocked 输入. 所有 flip-flops 是 重置 用 这

起作用的-低 碎片 输入, 重置

, 或者 在 这 配置

处理. 这 flip-flops share 这 使能 时钟 (ec) 这个,

当 低, recirculates 这 flip-flops’ 呈现 states 和

inhibits 回馈 至 这 数据-在 或者 combinatorial 函数

输入 在 一个 clb. 这 用户 将 使能 这些 控制 输入

和 选择 它们的 来源. 这 用户 将 也 选择 这

时钟 网 输入 (k), 作 好 作 它的 起作用的 sense 在里面 各自

clb. 这个 可编程序的 倒置 排除 这 需要 至

route 两个都 阶段 的 一个 时钟 信号 全部地 这 设备.

Q

COMBINATORIAL

函数

逻辑

变量

D

RD

G

F

DIN

F

G

QX

QY

DIN

F

G

G

QY

QX

F

QD

RD

使能 时钟

时钟

直接

重置

1 (使能)

一个

B

C

D

E

DI

EC

K

RD

Y

X

X3032

0 (inhibit)

(global 重置)

clb 输出

数据 在

0

1

0

1

MUX

MUX

图示 5: configurable 逻辑 块.

各自 clb 包含 一个 combinatorial 逻辑 部分, 二 flip-flops 和 一个 程序 记忆 控制 多路调制器 选择 的

函数. 它 有 这 下列的:

- five 逻辑 能变的 输入 一个, b, c, d, 和 e

- 一个 直接 数据 在 di

- 一个 使能 时钟 ec

- 一个 时钟 (invertible) k

- 一个 异步的 直接 重置 rd

- 二 输出 x 和 y