1

3.3 volt 高 密度 cmos

supersync fifo™

131,072 x 18

262,144 x 18

IDT72V295

IDT72V2105

dsc-4668/2

2001 整体的 设备 技术, 公司

这 supersync 先进先出 是 一个 商标 和 这 idt 标志 是 一个 注册 商标 的 整体的 设备 技术, 公司

•

choose among 这 下列的 记忆 organizations:

IDT72V295

131,072 x 18

IDT72V2105

262,144 x 18

•

管脚-兼容 和 这 idt72v255/72v265 和 这 idt72v275/

72v285 supersync fifos

•

10ns 读/写 循环 时间 (6.5ns 进入 时间)

•

fixed, 低 第一 文字 数据 latency 时间

•

5v 输入 tolerant

•

自动 电源 向下 降低 备用物品 电源 消耗量

•

主控 重置 clears 全部 先进先出

•

partial 重置 clears 数据, 但是 retains 可编程序的 settings

•

retransmit 运作 和 fixed, 低 第一 文字 数据 latency 时间

•

empty, 全部 和 half-全部 flags 信号 先进先出 状态

•

可编程序的 almost-empty 和 almost-全部 flags, 各自 标记 能

default 至 一个 的 二 preselected 补偿

•

程序 partial flags 用 也 串行 或者 并行的 意思

•

选择 idt 标准 定时 (使用

EF

和

FF

flags) 或者 第一 文字

下降 通过 定时 (使用

或者

和

IR

flags)

•

输出 使能 puts 数据 输出 在 高 阻抗 状态

•

容易地 expandable 在 depth 和 宽度

•

独立 读 和 写 clocks (准许 读 和 writing

同时发生地)

•

有 在 这 64-管脚 薄的 四方形 flat 包装 (tqfp)

•

高-效能 submicron cmos 技术

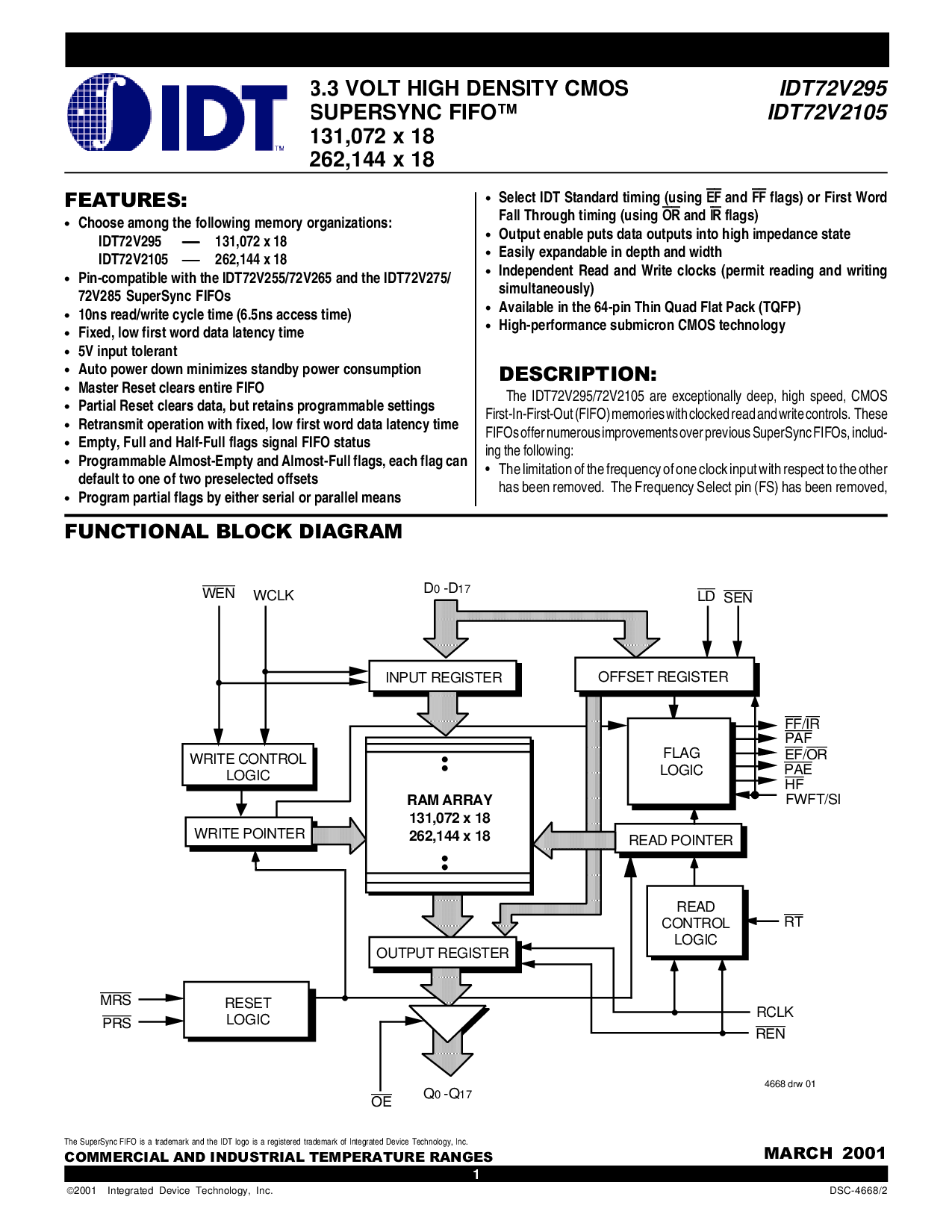

输入 寄存器

输出 寄存器

内存 排列

131,072 x 18

262,144 x 18

标记

逻辑

FF

/

IR

PAF

EF

/

或者

PAE

HF

读 pointer

读

控制

逻辑

写 控制

逻辑

写 pointer

重置

逻辑

WEN

WCLK

D

0

-d

17

LD

MRS

REN

RCLK

OE

Q

0

-q

17

补偿 寄存器

PRS

fwft/si

SEN

RT

4668 drw 01

这 idt72v295/72v2105 是 exceptionally 深的, 高 速, cmos

第一-在-第一-输出 (先进先出) memories 和 clocked 读 和 写 控制. 这些

fifos 提供 numerous 改进 在 previous supersync fifos, includ-

ing 这 下列的:

• 这 限制 的 这 频率 的 一个 时钟 输入 和 遵守 至 这 其它

有 被 移除. 这 频率 选择 管脚 (fs) 有 被 移除,