ics552-01

mds 552-01 c

1

修订 100104

整体的 电路 系统, 公司

●

525 race 街道, san jose, ca 95126

●

电话 (408) 297-1201

●

www.icst.com

振荡器, 乘法器, 和 缓存区 和 8 输出

描述

这 ics552-01 生产 8 低-skew copies 的 这

多样的 输入 时钟 或者 基本的, 并行的-模式

结晶. 不像 其它 时钟 驱动器, 这些 部分 做 不

需要 一个 独立的 振荡器 为 这 输入. 使用 ics’

专利的 阶段-锁 循环 (pll) 至 乘以 这

输入 频率, 它 是 完美的 为 generating 和

distributing 多样的 高-频率 clocks.

这个 是 一个

单独的 碎片 使用 为 3 不同的 产品:

1) ics552-01 (一个 模式) — 一个 振荡器 mutilpier

2) ics552-01 (b 模式) — 一个 双 1:4 缓存区

3) ics552-01 (c 模式) — 一个 1:8 振荡器 缓存区

特性 (所有)

•

packaged 作 20-管脚 ssop (qsop)

•

铅-自由 包装 有

•

运行 电压 的 3.0 v 至 5.5 v

•

工业的 温度 有

特性 (明确的)

ics552-01 (为 一个 模式)

•

包含 在-碎片 乘法器和 selections 的 x1,

x1.33, x2, x2.66, x3, x3.33, x4, x4.66, x5, 和 x6

•

电源-向下 和 触发-状态 模式

ics552-01 (为 b 模式)

•

向上 至 200 mhz 时钟 输入/输出 在 3.3 v

•

低 skew 的 250 ps 最大 为 任何 bank 的 四

•

输入 能 是 连接 一起 为 一个 1 至 8 缓存区

和 250 ps skew 在 任何 输出

•

非-反相的 缓存区 模式

•

完美的 为 时钟 网络

•

输出 使能 模式 触发-states 输出

•

全部 cmos 输出 摆动 和 25 毫安 输出 驱动

能力 在 ttl 水平

•

先进的, 低 电源, sub-micron cmosprocess

ics552-01 (为 c 模式)

•

使用 和 25 mhz 结晶 为 networking

•

使用 和 27 mhz 结晶 为 mpeg

ics552-01 (为 一个 和 c 模式)

•

输入 频率 的 10.0 至 27.0 mhz

•

提供 8 低-skew 输出 (<250 ps)

•

输出 时钟 职责 循环 的 40/60 在 3.3 v

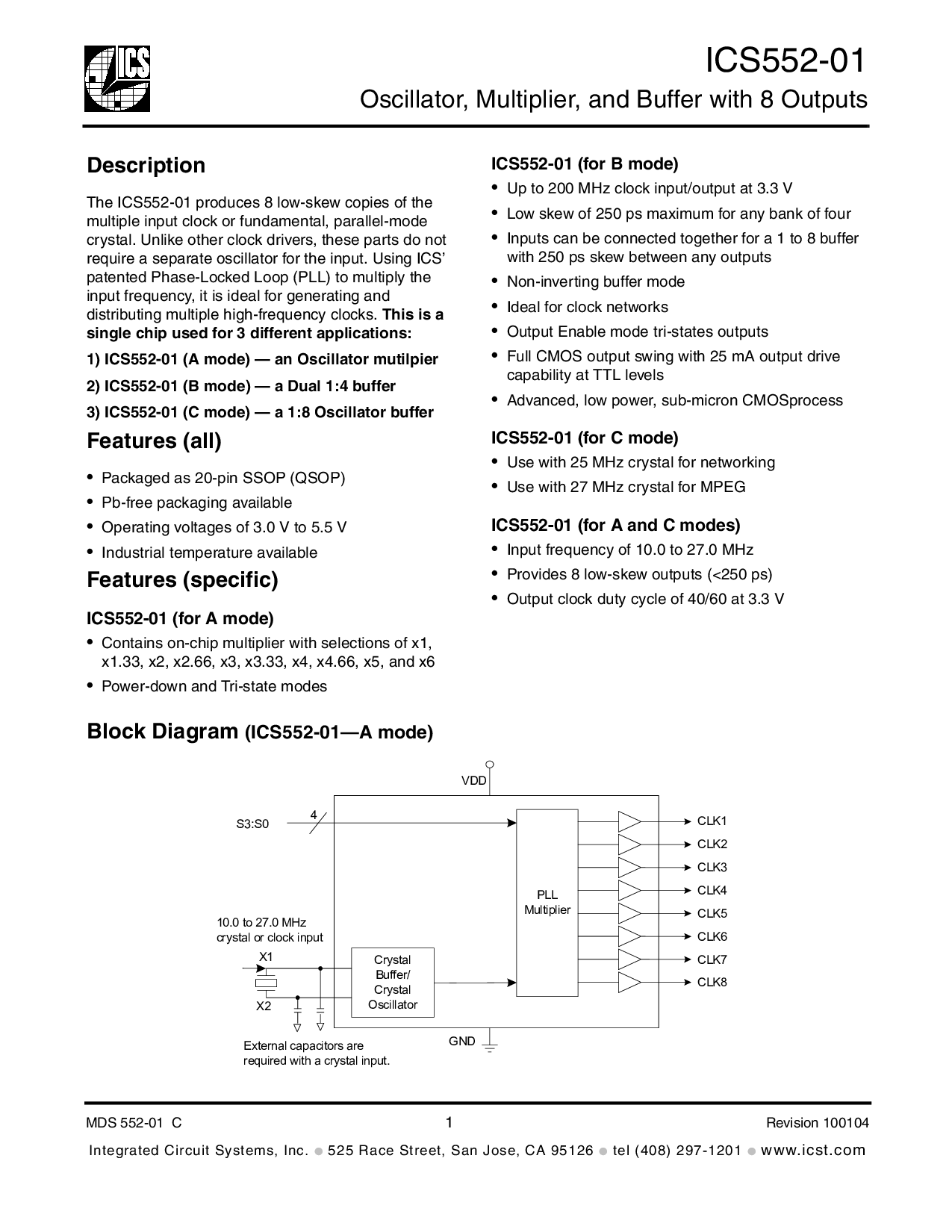

块 图解

(ics552-01—a 模式)

结晶

缓存区/

结晶

振荡器

地

VDD

PLL

乘法器

s3:s0

CLK1

CLK8

CLK7

CLK6

CLK5

CLK4

CLK3

CLK2

4

X2

10.0 至 27.0 mhz

结晶 或者 时钟 输入

外部 电容 是

必需的 和 一个 结晶 输入.

X1