L

OW

P

HASE

N

OISE

C

锁

M

ULTIPLIER

mds 601-01 l

2

修订 111204

整体的 电路 系统

●

525 race 街道, san jose, ca 95126

●

电话 (408) 297-1201

●

www.icst.com

ics601-01

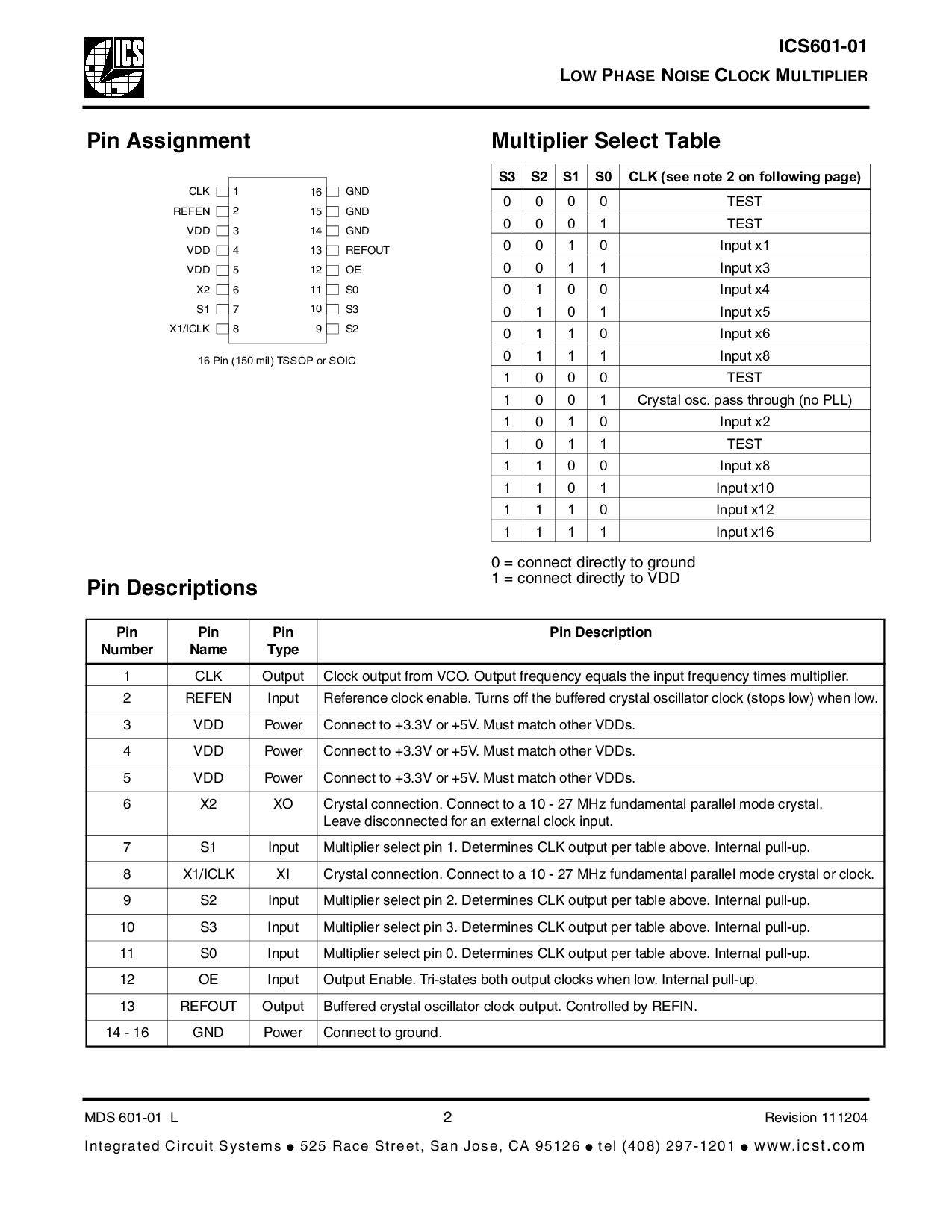

管脚 分派 乘法器 选择 表格

0 = 连接 直接地 至 地面

1 = 连接 直接地 至 vdd

管脚 描述

1

2

3

VDD

4

REFEN

5

6

地

7

8

地

REFOUT

S3S1

地

X2

S2

VDD

16

CLK

VDD

x1/iclk

S0

OE

15

14

13

12

11

10

9

16 管脚 (150 mil) tssop 或者 soic

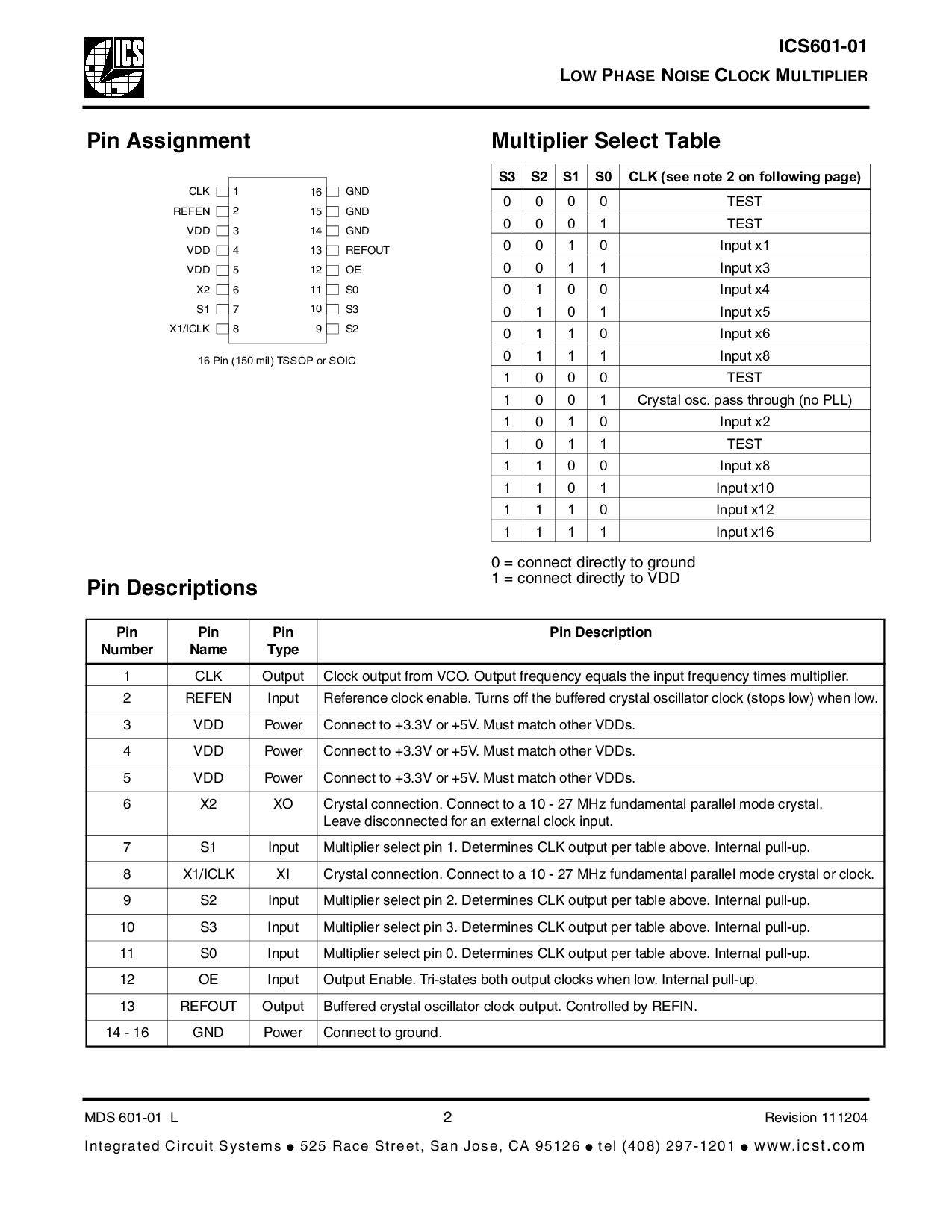

S3 S2

S1 S0 clk (看 便条 2 在 下列的 页)

00

0 0 测试

00

0 1 测试

00

1 0 输入 x1

00

1 1 输入 x3

01

0 0 输入 x4

01

0 1 输入 x5

01

1 0 输入 x6

01

1 1 输入 x8

10

0 0 测试

10

0 1 结晶 osc. 通过 通过 (非 pll)

10

1 0 输入 x2

10

1 1 测试

11

0 0 输入 x8

11

0 1 输入 x10

11

1 0 输入 x12

11

1 1 输入 x16

管脚

号码

管脚

名字

管脚

典型值e

管脚 描述

1 CLK 输出 时钟 输出 从 vco. 输出 frequency 相等 这 输入 频率 时间 乘法器.

2 REFEN 输入 涉及 时钟 使能. 转变 止 这 缓冲 结晶 振荡器 时钟 (stops 低) 当 低.

3 VDD 电源 连接 至 +3.3v 或者 +5v. 必须 相一致 其它 vdds.

4 VDD 电源 连接 至 +3.3v 或者 +5v. 必须 相一致 其它 vdds.

5 VDD 电源 连接 至 +3.3v 或者 +5v. 必须 相一致 其它 vdds.

6 X2 XO 结晶 连接. 连接 至 一个 10 - 27 mhz 基本的 并行的 模式 结晶.

leave disconnected 为 一个 外部 时钟 输入.

7 S1 输入 乘法器 选择 管脚 1. 确定 clk 输出 每 表格 在之上. 内部的 拉-向上.

8 x1/iclk XI 结晶 连接. 连接 至 一个 10 - 27 mhz 基本的 并行的 模式 结晶 或者 时钟.

9 S2 输入 乘法器 选择 管脚 2. 确定 clk 输出 每 表格 在之上. 内部的 拉-向上.

10 S3 输入 乘法器 选择 管脚 3. 确定 clk 输出 每 表格 在之上. 内部的 拉-向上.

11 S0 输入 乘法器 选择 管脚 0. 确定 clk 输出 每 表格 在之上. 内部的 拉-向上.

12 OE 输入 输出 使能. 触发-states 两个都 输出 clocks 当 低. 内部的 拉-向上.

13 REFOUT 输出 缓冲 结晶 振荡器 时钟 输出. 控制 用 refin.

14 - 16 地 电源 连接 至 地面.