#### January 2006

## DS90C241/DS90C124 5-35MHz DC-Balanced 24-Bit LVDS Serializer and Deserializer

#### **General Description**

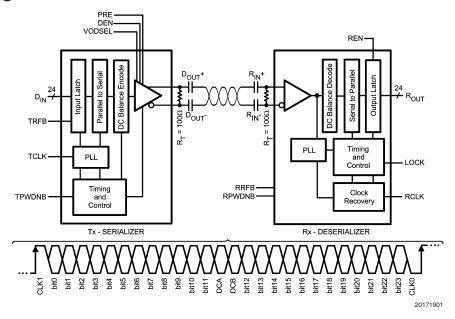

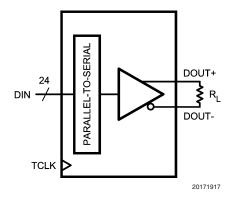

The DS90C241/124 Chipset translates a 24-bit parallel bus into a fully transparent data/control LVDS serial stream with embedded clock information. This single serial stream simplifies transferring a 24-bit bus over PCB traces and cable by eliminating the skew problems between parallel data and clock paths. It saves system cost by narrowing data paths that in turn reduce PCB layers, cable width, and connector size and pins.

The DS90C241/124 incorporates LVDS signaling on the high-speed I/O. LVDS provides a low power and low noise environment for reliably transferring data over a serial transmission path. By optimizing the serializer output edge rate for the operating frequency range EMI is further reduced.

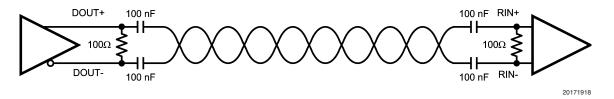

In addition the device features pre-emphasis to boost signals over longer distances using lossy cables. Internal DC balanced encoding/decoding is used to support AC-Coupled interconnects.

#### **Features**

- 5 MHz-35 MHz clock embedded and DC-Balancing 1:24 and 24:1 data transmissions

- User defined pre-emphasis driving ability through external resistor on LVDS outputs and capable to drive up to 10 meters shielded twisted-pair cable

- User selectable clock edge for parallel data on both TX and RX

- Supports AC-coupling interface

- Individual power-down controls for both TX and RX

- Embedded clock CDR (clock and data recovery) on RX and no external source of reference clock needed

- All codes RDL (random data lock) to support hot-pluggable applications

- LOCK output flag to ensure data integrity at RX side

- Balanced T<sub>SETUP</sub>/T<sub>HOLD</sub> between RCLK and RDATA on RX side

- PTO (progressive turn-on) LVTTL O/P to minimize the SSO effects

- All LVTTL inputs and control pins have internal pulldown except PRE

- On-chip filters for PLLs on TX and RX

- 48 pin TQFP package for both TX and RX

- Pure CMOS .35 µm process

- Power supply range 3.3V ± 10%

- Temperature range -40°C to +105°C

- 8 kV HBM ESD structure

### **Block Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{CC}$ ) = -0.3V to +4V LVCMOS/LVTTL Input Voltage = -0.3V to ( $V_{CC}$  +0.3V)

LVCMOS/LVTTL Output

$\begin{array}{lll} \mbox{Voltage} & -0.3 \mbox{V to (V}_{\mbox{\scriptsize CC}} + 0.3 \mbox{V}) \\ \mbox{LVDS Receiver Input Voltage} & -0.3 \mbox{V to } 3.9 \mbox{V} \\ \mbox{LVDS Driver Output Voltage} & -0.3 \mbox{V to } 3.9 \mbox{V} \\ \end{array}$

LVDS Output Short Circuit

Duration 10 ms Junction Temperature  $+150^{\circ}$ C Storage Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C

Lead Temperature

(Soldering, 4 seconds) +260°C

Maximum Package Power Dissipation Capacity Package

De-rating:

48L TQFP  $1/\theta_{JA}$  °CW above +25°C

DS90C241

θ<sub>JA</sub> 45.8 (4L\*); 75.4 (2L\*) °C/W

$\theta_{JC}$  21.0°C/W

DS90C124

$\theta_{JA}$  45.4 (4L\*); 75.0 (2L\*)°C/W  $\theta_{JC}$  21.1°C/W

\*JEDEC

ESD Rating (HBM) >8 kV

ESD Rating (ISO10605) DS90C241 meets ISO 10605

Contact Discharge ( $D_{OUT+}$ ,  $D_{OUT-}$ ) to GND  $\pm 10 \text{ kV}$ Air Discharge ( $D_{OUT+}$ ,  $D_{OUT-}$ ) to GND  $\pm 30 \text{ kV}$

## Recommended Operating Conditions

|                                   | Min | Nom | Max  | Units      |

|-----------------------------------|-----|-----|------|------------|

| Supply Voltage (V <sub>CC</sub> ) | 3.0 | 3.3 | 3.6  | V          |

| Operating Free Air                |     |     |      |            |

| Temperature (T <sub>A</sub> )     | -40 | +25 | +105 | °C         |

| Clock Rate                        | 5   |     | 35   | MHz        |

| Supply Noise                      |     |     | ±100 | $mV_{P-P}$ |

|                                   |     |     |      |            |

#### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol          | Parameter                    | Conditions                                  | Pin/Freq.                           | Min  | Тур  | Max             | Units |

|-----------------|------------------------------|---------------------------------------------|-------------------------------------|------|------|-----------------|-------|

| LVCMO           | S/LVTTL DC SPECIFICATION     | S                                           |                                     |      |      |                 |       |

| V <sub>IH</sub> | High Level Voltage           |                                             | Tx: DIN[0:23], TCLK,                | 2.0  |      | V <sub>CC</sub> | V     |

| V <sub>IL</sub> | Low Level Input Voltage      |                                             | DEN, TRFB, DCAOFF,                  | GND  |      | 0.8             | V     |

| V <sub>CL</sub> | Input Clamp Voltage          | I <sub>CL</sub> = -18 mA                    | DCBOFF, VODSEL                      |      | -0.7 | -1.2            | V     |

| I <sub>IN</sub> | Input Current                | V <sub>IN</sub> = 0V or 3.6V                | Rx: RRFB, REN                       | -10  | ±2   | +10             | μΑ    |

|                 |                              |                                             | Tx: TPWDNB Rx: RPWDNB               | -20  | ±5   | +20             | μА    |

| V <sub>OH</sub> | High Level Output Voltage    | $I_{OH} = -2 \text{ mA}$                    | ROUT[0:23], RCLK,                   | 2.3  | 3.0  | V <sub>CC</sub> | V     |

| V <sub>OL</sub> | Low Level Output Voltage     | I <sub>OL</sub> = +2 mA                     | LOCK                                | GND  | 0.33 | 0.5             | V     |

| Ios             | Output Short Circuit Current | $V_{OUT} = 0V$                              |                                     |      |      | -110            | mA    |

| l <sub>oz</sub> | TRI-STATE® Output Current    | RPWRDN = 0.8V,                              | ROUT[0:23], RCLK,                   | -15  | ±0.4 | +15             | μA    |

|                 |                              | $V_{OUT} = 0V \text{ or } V_{CC}$           | LOCK                                | _13  | ±0.4 | +13             | μΑ    |

| LVDS D          | C SPECIFICATIONS             |                                             |                                     |      |      |                 |       |

| $V_{TH}$        | Differential Threshold High  | $V_{CM} = +1.2V$                            | R <sub>IN+</sub> , R <sub>IN-</sub> |      |      | +100            | mV    |

|                 | Voltage                      |                                             |                                     |      |      | 1100            |       |

| $V_{TL}$        | Differential Threshold Low   |                                             |                                     | -100 |      |                 | mV    |

|                 | Voltage                      |                                             |                                     | 100  |      |                 | 1111  |

| I <sub>IN</sub> | Input Current                | $V_{IN} = 2.4V,$                            |                                     |      |      | ±100            | μA    |

|                 |                              | V <sub>CC</sub> = 3.6V or 0V                |                                     |      |      |                 | μ, (  |

|                 |                              | $V_{IN} = 0V, V_{CC} = 3.6V \text{ or } 0V$ |                                     |      |      | ±100            | μΑ    |

#### **Electrical Characteristics** (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                                                                                                                  | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pin/Freq.                             | Min          | Тур              | Max           | Units |

|-------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|------------------|---------------|-------|

| LVDS D            | C SPECIFICATIONS                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |              |                  | •             |       |

| V <sub>OD</sub>   | Output Differential Voltage (D <sub>OUT+</sub> )-(D <sub>OUT-</sub> ) ( <i>Figure 16</i> )                                 | $R_L = 100\Omega$ , w/o pre-emphasis<br>VODSEL = L<br>(VODSEL = H)                                                                                                                                                                                                                                                                                                                                                                                                  | D <sub>OUT+</sub> , D <sub>OUT-</sub> | 250<br>(500) | 400<br>(800)     | 600<br>(1200) | mV    |

| $\Delta V_{OD}$   | Output Differential Voltage<br>Unbalance                                                                                   | $R_L = 100\Omega$ , w/o pre-emphasis                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |              | 10               | 50            | mV    |

| V <sub>os</sub>   | Offset Voltage                                                                                                             | $R_L = 100\Omega$ , w/o pre-emphasis                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | 1.05         | 1.2              | 1.25          | V     |

| $\Delta V_{OS}$   | Offset Voltage Unbalance                                                                                                   | $R_L = 100\Omega$ , w/o pre-emphasis                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |              | 10               | 50            | mV    |

| I <sub>os</sub>   | Output Short Circuit Current                                                                                               | DOUT = 0V, DIN = H,<br>TPWRDND = 2.4V                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       | -35          | -50              | -70           | mA    |

| l <sub>oz</sub>   | TRI-STATE Output Current                                                                                                   | TPWRDND = 0.8V,<br>DOUT = 0V or V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | -10          | ±1               | 10            | μА    |

| SER/DE            | S SUPPLY CURRENT (DVDD                                                                                                     | *, PVDD* and AVDD* pins) <i>*Digi</i> t                                                                                                                                                                                                                                                                                                                                                                                                                             | tal, PLL, and Analog VDDs             | •            |                  |               |       |

| Ісст              | Serializer (Tx) Total Supply Current (includes load current)  Serializer (Tx) Total Supply Current (includes load current) | $\begin{aligned} R_L &= 100\Omega \\ \text{Pre-emphasis} &= \text{OFF} \\ \text{Checker-board pattern} \\ \text{VODSEL=L } (\textit{Figure 1}) \\ R_L &= 100\Omega \\ \text{RPRE} &= 6 \text{ k}\Omega \\ \text{Checker-board pattern} \\ \text{VODSEL=L } (\textit{Figure 1}) \\ R_L &= 100\Omega \\ R_{PRE} &= \text{OFF} \\ \text{Random pattern} \\ \text{VODSEL=L} \\ R_L &= 100\Omega \\ R_{PRE} &= 6 \text{ k}\Omega \\ \text{Random pattern} \end{aligned}$ | f = 35 MHz  f = 35 MHz  f = 35 MHz    |              | 105<br>120<br>65 |               | mA mA |

| I <sub>CCTZ</sub> | Serializer (Tx) Supply Current Power-down                                                                                  | VODSEL=L<br>TPWRDNB = 0.8V                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |              | 200              | 500           | μА    |

| I <sub>CCR</sub>  | Deserializer (Rx) Total Supply Current (includes load current)                                                             | C <sub>L</sub> = 8 pF<br>Checker-board pattern<br>LVTTL Output <i>(Figure 2)</i>                                                                                                                                                                                                                                                                                                                                                                                    | f = 35 MHz                            |              | 180              |               | mA    |

|                   | Deserializer (Rx) Total Supply Current (includes load current)                                                             | C <sub>L</sub> = 8 pF<br>Random pattern<br>LVTTL Output                                                                                                                                                                                                                                                                                                                                                                                                             | f = 35 MHz                            |              | 110              |               | mA    |

| I <sub>CCRZ</sub> | Deserializer (Rx)<br>Supply Current Power-down                                                                             | RPWRDND = 0.8V                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |              | 500              | 750           | μА    |

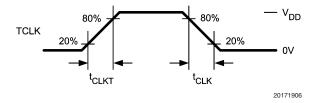

## **Serializer Timing Requirements for TCLK**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                  | Conditions | Min  | Тур  | Max  | Units |

|-------------------|----------------------------|------------|------|------|------|-------|

| t <sub>TCP</sub>  | Transmit Clock Period      |            | 28.6 | Т    | 200  | ns    |

| t <sub>TCIH</sub> | Transmit Clock High Time   |            | 0.4T | 0.5T | 0.6T | ns    |

| t <sub>TCIL</sub> | Transmit Clock Low Time    |            | 0.4T | 0.5T | 0.6T | ns    |

| t <sub>CLKT</sub> | TCLK Input Transition Time |            |      | 3    | 6    | ns    |

| t <sub>JIT</sub>  | TCLK Input Jitter          | (Note 9)   |      |      | ±200 | ns    |

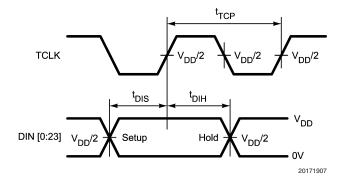

## Serializer Switching Characteristics Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                           | Conditions                                         | Min | Тур         | Max | Units |

|-------------------|-------------------------------------|----------------------------------------------------|-----|-------------|-----|-------|

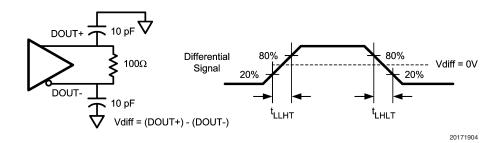

| t <sub>LLHT</sub> | LVDS Low-to-High Transition Time    | $R_L = 100\Omega,$<br>$C_L = 10 \text{ pF to GND}$ |     | 0.6         |     | ns    |

| t <sub>LHLT</sub> | LVDS High-to-Low Transition Time    | VODSEL = L<br>(Figure 3)                           |     | 0.6         |     | ns    |

| t <sub>DIS</sub>  | DIN (0:23) Setup to TCLK            | $R_L = 100\Omega$ ,                                | 5   |             |     | ns    |

| t <sub>DIH</sub>  | DIN (0:23) Hold from TCLK           | $C_L = 10 \text{ pF to GND}$<br>(Note 8)           | 5   |             |     | ns    |

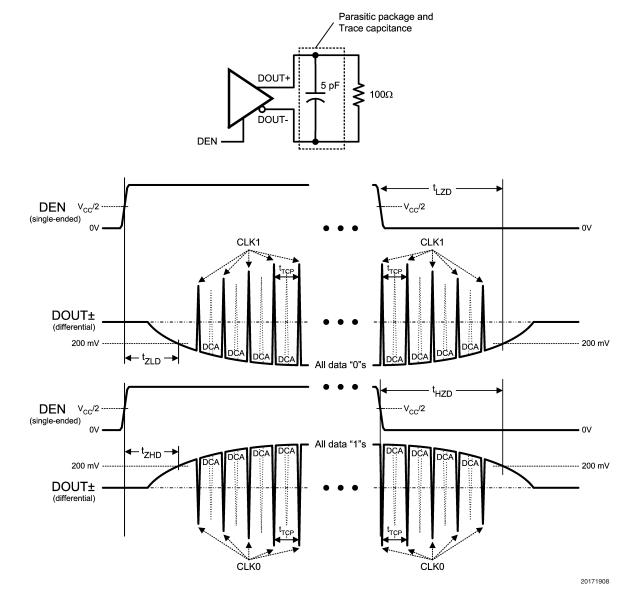

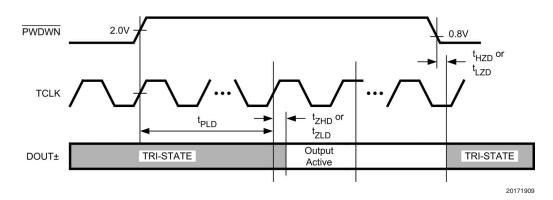

| t <sub>HZD</sub>  | DOUT ± HIGH to TRI-STATE Delay      | $R_L = 100\Omega$ ,                                |     | 5           |     | ns    |

| t <sub>LZD</sub>  | DOUT ± LOW to TRI-STATE Delay       | $C_L = 10 \text{ pF to GND}$                       |     | 5           |     | ns    |

| t <sub>zhD</sub>  | DOUT ± TRI-STATE to HIGH Delay      | (Note 4) (Figure 7)                                |     | 5           |     | ns    |

| t <sub>ZLD</sub>  | DOUT ± TRI-STATE to LOW Delay       |                                                    |     | 5           |     | ns    |

| t <sub>PLD</sub>  | Serializer PLL Lock Time (Figure 8) | $R_L = 100\Omega$                                  |     | 10          |     | ms    |

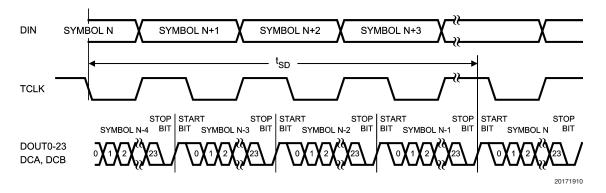

| t <sub>SD</sub>   | Serializer Delay (Figure 9)         | $R_L = 100\Omega$<br>VODSEL = L, TRFB = H          |     | 3.5T + 2.85 |     | ns    |

|                   |                                     | $R_L = 100\Omega$<br>VODSEL = L, TRFB = L          |     | 3.5T + 2.85 |     | ns    |

# **Deserializer Switching Characteristics**Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol           | Parameter                                                                                       | Conditions                              | Pin/Freq.                  | Min                        | Тур                        | Max                        | Units |

|------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------|----------------------------|----------------------------|----------------------------|-------|

| t <sub>RCP</sub> | Receiver out Clock Period (Note 8)                                                              | $t_{RCP} = t_{TCP}$                     | RCLK                       | 28.6                       |                            | 200                        | ns    |

| t <sub>RDC</sub> | RCLK Duty Cycle                                                                                 |                                         | RCLK                       | 45                         | 50                         | 55                         | %     |

| t <sub>CLH</sub> | CMOS/TTL Low-to-High<br>Transition Time                                                         | C <sub>L</sub> = 8 pF<br>(lumped load)  | ROUT [0:23],<br>LOCK, RCLK |                            | 2.5                        | 3.5                        | ns    |

| t <sub>CHL</sub> | CMOS/TTL High-to-Low<br>Transition Time                                                         | (Figure 4)                              |                            |                            | 2.5                        | 3.5                        | ns    |

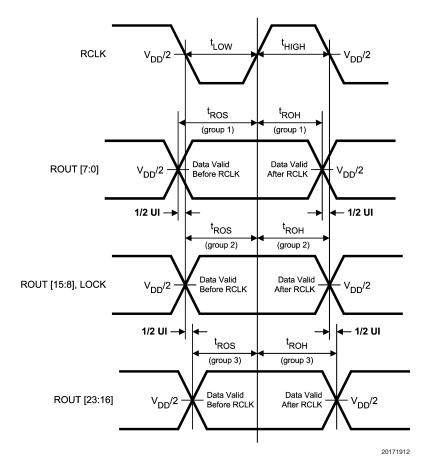

| t <sub>ROS</sub> | ROUT (0:7) Setup Data to  RCLK (Group 1)  (Figure 11)  ROUT [0:7]  (29/56)*t <sub>RCP</sub>     |                                         |                            |                            |                            | (2/5)*<br>t <sub>RCP</sub> | ns    |

| t <sub>ROH</sub> | ROUT (0:7) Hold Data to<br>RCLK (Group 1)<br>(Figure 11)                                        |                                         |                            |                            | (27/56)*t <sub>RCP</sub>   | (2/5)*<br>t <sub>RCP</sub> | ns    |

| t <sub>ROS</sub> | ROUT (8:15) Setup Data to<br>RCLK (Group 2)<br>(Figure 11)                                      | CLK (Group 2) LOCK 0.5*t <sub>RCP</sub> |                            |                            | (2/5)*<br>t <sub>RCP</sub> | ns                         |       |

| t <sub>кон</sub> | ROUT (9:15) Hold Data to<br>RCLK (Group 2)<br>(Figure 11)                                       |                                         |                            | 0.5*t <sub>RCP</sub>       |                            |                            | ns    |

| t <sub>ROS</sub> | ROUT (16:23) Setup Data to  RCLK (Group 3)  (Figure 11)  ROUT [16:23]  (27/56)*t <sub>RCP</sub> |                                         |                            | (2/5)*<br>t <sub>RCP</sub> | ns                         |                            |       |

| t <sub>вон</sub> | ROUT (16:23) Hold Data to RCLK (Group 3) (Figure 11)  (29/56)*t <sub>RCP</sub>                  |                                         |                            | (2/5)*<br>t <sub>RCP</sub> | ns                         |                            |       |

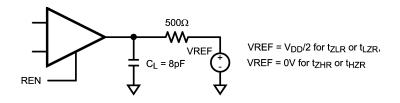

| t <sub>HZR</sub> | HIGH to TRI-STATE Delay (Figure 12) ROUT [0:23], 3                                              |                                         |                            |                            | 3                          | 10                         | ns    |

| t <sub>LZR</sub> | LOW to TRI-STATE Delay                                                                          |                                         | RCLK, LOCK                 |                            | 3                          | 10                         | ns    |

| t <sub>zhr</sub> | TRI-STATE to HIGH Delay                                                                         |                                         |                            |                            | 3                          | 10                         | ns    |

| t <sub>zLR</sub> | TRI-STATE to LOW Delay                                                                          |                                         |                            |                            | 3                          | 10                         | ns    |

#### **Descrializer Switching Characteristics** (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                                      | Conditions    | Pin/Freq.    | Min | Тур          | Max  | Units |

|-------------------|------------------------------------------------|---------------|--------------|-----|--------------|------|-------|

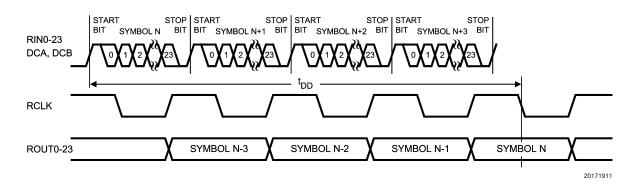

| t <sub>DD</sub>   | Deserializer Delay                             |               | RCLK         |     | [4+(3/56)]T+ |      | ns    |

|                   | (Figure 10)                                    |               | NOLK         |     | 5.9          |      |       |

|                   |                                                |               | 5 MHz        |     | 817          | 825  | ns    |

|                   |                                                |               | 35 MHz       |     | 122          | 125  | ns    |

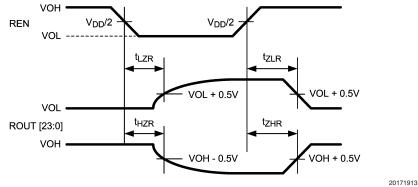

| t <sub>DRDL</sub> | Deserializer PLL Lock Time                     | (Notes 7, 8)  | 5 MHz        |     | 5            | 12   | ms    |

|                   | from Powerdown                                 |               | 35 MHz       |     | 5            | 10   | ms    |

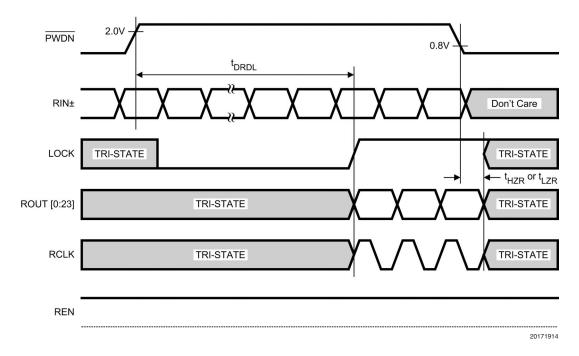

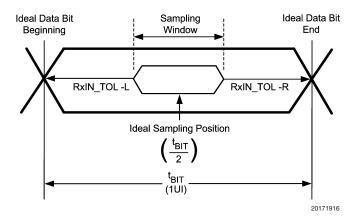

| RxIN_TOL_L        | Receiver INput TOLerance<br>Left, (Figure 15)  | (Notes 6, 10) | 5 MHz-35 MHz |     |              | 0.25 | UI    |

| RxIN_TOL_R        | Receiver INput TOLerance<br>Right, (Figure 15) | (Notes 6, 10) | 5 MHz-35 MHz |     |              | 0.25 | UI    |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

Note 2: Typical values are given for  $V_{CC}$  = 3.3V and  $T_A$  = +25°C.

Note 3: Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except VOD,  $\Delta$ VOD, VTH and VTL which are differential voltages.

Note 4: When the Serializer output is tri-stated, the Deserializer will lose PLL lock. Resynchronization MUST occur before data transfer.

Note 5: tDRDL is the time required by the deserializer to obtain lock when exiting powerdown mode. tDRDL is specified with an external synchronization pattern.

Note 6: RxIN\_TOL is a measure of how much phase noise (jitter) the deserializer can tolerate in the incoming data stream before bit errors occur. It is a measurement in reference with the ideal bit position, please see National's AN-1217 for detail.

Note 7: The Deserializer PLL lock time may vary depending on input data patterns and the number of transitions within the pattern.

Note 8: Guaranteed by Design (GBD) using statistical analysis.

Note 9: Total Interconnect Jitter Budget (t,j) specifies the allowable jitter added by the interconnect assuming both transmitter and receiver are Auto SerDes circuits.

Note 10: UI - Unit Interval, equivalent to one ideal serialized data bit width. The UI scales with frequency.

Note 11: Figures 1, 2, 9, 10, 13 show a falling edge data strobe (TCLK IN/RCLK OUT).

Note 12: Figures 6, 11 show a rising edge data strobe (TCLK IN/RCLK OUT).

## **AC Timing Diagrams and Test Circuits**

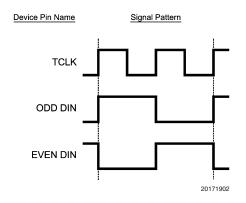

FIGURE 1. Serializer Input Checker-board Pattern

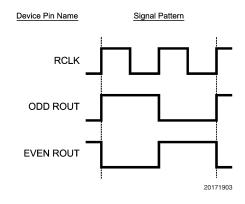

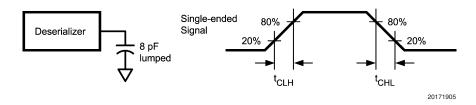

FIGURE 2. Deserializer Output Checker-board Pattern

FIGURE 3. Serializer LVDS Output Load and Transition Times

FIGURE 4. Deserializer LVCMOS/LVTTL Output Load and Transition Times

FIGURE 5. Serializer Input Clock Transition Times

FIGURE 6. Serializer Setup/Hold Times

FIGURE 7. Serializer TRI-STATE Test Circuit and Delay

FIGURE 8. Serializer PLL Lock Time, and TPWDNB TRI-STATE Delays

FIGURE 9. Serializer Delay

FIGURE 10. Deserializer Delay

FIGURE 11. Deserializer Setup and Hold Times

Note: C<sub>L</sub> includes instrumentation and fixture capacitance within 6 cm of ROUT[23:0]

FIGURE 12. Deserializer TRI-STATE Test Circuit and Timing

FIGURE 13. Deserializer PLL Lock Times and RPWDNB TRI-STATE Delay

FIGURE 14. Transmitter Output Eye Opening

FIGURE 15. Receiver Input Tolerance (RxIN\_TOL) and Sampling Window

$VOD = (D_{OUT+}) - (D_{OUT-})$

Differential output signal is shown as  $(D_{OUT+}) - (D_{OUT-})$ , device in Data Transfer mode.

FIGURE 16. Serializer VOD Diagram

FIGURE 17. AC Coupled Application

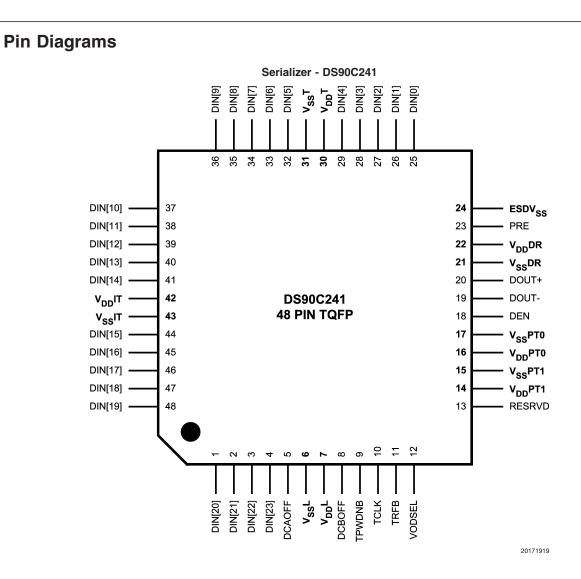

| Pin #  | Pin Name      | I/O          | Description                                                                                          |

|--------|---------------|--------------|------------------------------------------------------------------------------------------------------|

| DS90C  | 241 SERIALIZE | R PIN DESCR  | RIPTIONS                                                                                             |

| 22     | VDDDR         | VDD          | Analog Voltage Supply, LVDS O/P Power                                                                |

| 21     | VSSDR         | GND          | Analog Ground, LVDS O/P Ground                                                                       |

| 16     | VDDPT0        | VDD          | Analog Voltage supply, VCO Power                                                                     |

| 17     | VSSPT0        | GND          | Analog ground, VCO Ground                                                                            |

| 14     | VDDPT1        | VDD          | Analog Voltage supply, PLL Power                                                                     |

| 15     | VSSPT1        | GND          | Analog Ground, PLL Ground                                                                            |

| 30     | VDDT          | VDD          | Digital Voltage supply, Tx serializer Power                                                          |

| 31     | VSST          | GND          | Digital Ground, Tx serializer Ground                                                                 |

| 7      | VDDL          | VDD          | Digital Voltage supply, Tx Logic Power                                                               |

| 6      | VSSL          | GND          | Digital Ground, Tx Logic <b>G</b> round                                                              |

| 42     | VDDIT         | VDD          | Digital Voltage supply, Tx Input Power                                                               |

| 43     | VSSIT         | GND          | Digital Ground, Tx Input Ground                                                                      |

| 24     | VSSESD        | GND          | ESD Ground                                                                                           |

| 4-1,   | DIN[23:0]     | CMOS_I       | Transmitter Data INputs                                                                              |

| 48-44, |               |              |                                                                                                      |

| 41-32, |               |              |                                                                                                      |

| 29-25  |               |              |                                                                                                      |

| 10     | TCLK          | CMOS_I       | Transmitter reference CLocK.                                                                         |

|        |               |              | Used to strobe data at the DIN inputs and to drive the transmitter PLL                               |

| 9      | TPWDNB        | CMOS_I       | Transmitter PoWer DowN Bar (ACTIVE L).                                                               |

|        |               |              | TPWDNB = L; Disabled, DOUT (+/-) are TRI-STATED stand-by mode, PLL is shutdown                       |

|        | 551           | 01100        | TPWDNB = H; Enabled                                                                                  |

| 18     | DEN           | CMOS_I       | Data ENable (ACTIVE H)                                                                               |

|        |               |              | DEN = L; Disabled, DOUT (+/-) are TRI-STATED, PLL still operational DEN = H; Enabled                 |

| 13     | RESRVD        | CMOS_I       | RESERVED - tie Low                                                                                   |

| 23     | PRE           | CMOS_I       | PRE-emphasis select pin.                                                                             |

| 20     | ' ' '         | OWIGO_I      | PRE = $(R_{PRE} \ge 3 \text{ k}\Omega)$ ; $I_{max} = (1.2/R*20)$ , $R_{min} = 3 \text{ k}\Omega$     |

|        |               |              | PRE = H or floating; pre-emphasis off                                                                |

| 11     | TRFB          | CMOS_I       | Transmitter Rising/Falling Bar Clock Edge Select (H = rising edge L = falling edge)                  |

| 12     | VODSEL        | CMOS_I       | VOD level SELect                                                                                     |

|        |               | _            | VODSEL = L; IOD ≈ 3.5 mA, (default). e.g. 3.5 mA*100Ω≈350 mV                                         |

|        |               |              | VODSEL = H; IOD $\approx$ 7.0 mA, VOD doubles approximately. e.g. 7 mA*100 $\Omega$ $\approx$ 700 mV |

| 5      | DCAOFF        | CMOS_I       | RESERVED — tie Low                                                                                   |

| 8      | DCBOFF        | CMOS_I       | RESERVED — tie Low                                                                                   |

| 20     | DOUT+         | LVDS_O       | Transmitter LVDS true (+) OUTput                                                                     |

| 19     | DOUT-         | LVDS_O       | Transmitter LVDS inverted (-) OUTput                                                                 |

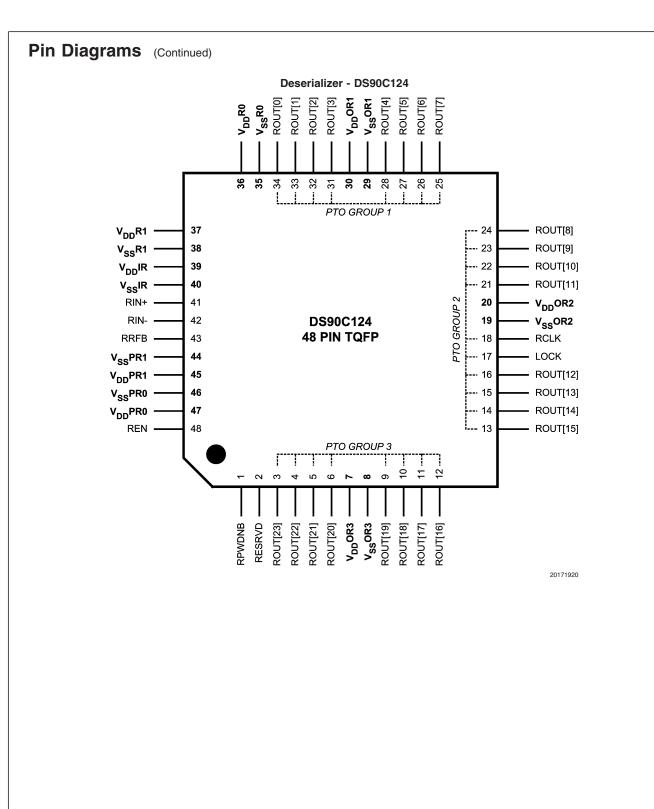

| DS90C  | 124 DESERIAL  | IZER PIN DES | SCRIPTIONS                                                                                           |

| 39     | VDDIR         | VDD          | Analog LVDS Voltage supply, Power                                                                    |

| 40     | VSSIR         | GND          | Analog LVDS <b>G</b> round                                                                           |

| 47     | VDDPR0        | VDD          | Analog Voltage supply, PLL Power                                                                     |

| 46     | VSSPR0        | GND          | Analog Ground, PLL Ground                                                                            |

| 45     | VDDPR1        | VDD          | Analog Voltage supply, PLL VCO Power                                                                 |

| 44     | VSSPR1        | GND          | Analog Ground, PLL VCO Ground                                                                        |

| 37     | VDDR1         | VDD          | Digital Voltage supply, Logic Power                                                                  |

| 38     | VSSR1         | GND          | Digital Ground, Logic Ground                                                                         |

| 36     | VDDR0         | VDD          | Digital <b>V</b> oltage supply, Logic Power                                                          |

| 35     | VSSR0         | GND          | Digital Ground, Logic Ground                                                                         |

| 30     | VDDOR1        | VDD          | Digital Voltage supply, LVTTL O/P Power                                                              |

## Pin Descriptions (Continued)

| Pin #           | Pin Name      | I/O          | Description                                                                                                                                                |

|-----------------|---------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS90C           | 124 DESERIALI | ZER PIN DESC | CRIPTIONS                                                                                                                                                  |

| 29              | VSSOR1        | GND          | Digital Ground, LVTTL O/P Ground                                                                                                                           |

| 20              | VDDOR2        | VDD          | Digital Voltage supply, LVTTL O/P Power                                                                                                                    |

| 19              | VSSOR2        | GND          | Digital Ground, LVTTL O/P Ground                                                                                                                           |

| 7               | VDDOR3        | VDD          | Digital Voltage supply, LVTTL O/P Power                                                                                                                    |

| 8               | VSSOR3        | GND          | Digital Ground, LVTTL O/P Ground                                                                                                                           |

| 41              | RIN+          | LVDS_I       | Receiver LVDS true (+) INput                                                                                                                               |

| 42              | RIN-          | LVDS_I       | Receiver LVDS inverted (-) INput                                                                                                                           |

| 2               | RESRVD        | CMOS_I       | RESERVED - tie Low                                                                                                                                         |

| 43              | RRFB          | CMOS_I       | Receiver Rising Falling Bar clock Edge Select RRFB = H; ROUT LVTTL O/P clocked on Rising CLK RRFB = L; ROUT LVTTL O/P clocked on Falling CLK               |

| 48              | REN           | CMOS_I       | Receiver ENable, (ACTIVE H) REN = L; Disabled, ROUT[23-0] and RCLK TRI-STATED, PLL still operational REN = H; Enabled                                      |

| 1               | RPWDNB        | CMOS_I       | Receiver PoWer DowN Bar (ACTIVE L)  RPWDNB = L; Disabled, ROUT[23-0], RCLK, and LOCK are TRI-STATED in stand-by mode, PLL is shutdown  RPWDNB = H; Enabled |

| 17              | LOCK          | CMOS_O       | LOCK indicates the status of the receiver PLL  LOCK = L; receiver PLL is unlocked, ROUT[23-0] and RCLK are TRI-STATED  LOCK = H; receiver PLL is locked    |

| 25-28,<br>31-34 | ROUT[7:0]     | CMOS_O       | Receiver Outputs – Group 1                                                                                                                                 |

| 13-16,<br>21-24 | ROUT[15:8]    | CMOS_O       | Receiver Outputs – Group 2                                                                                                                                 |

| 3-6,<br>9-12    | ROUT[23:16]   | CMOS_O       | Receiver Outputs – Group 3                                                                                                                                 |

| 18              | RCLK          | CMOS_O       | Recovered CLocK. Parallel data rate clock recovered from the embedded clock.                                                                               |

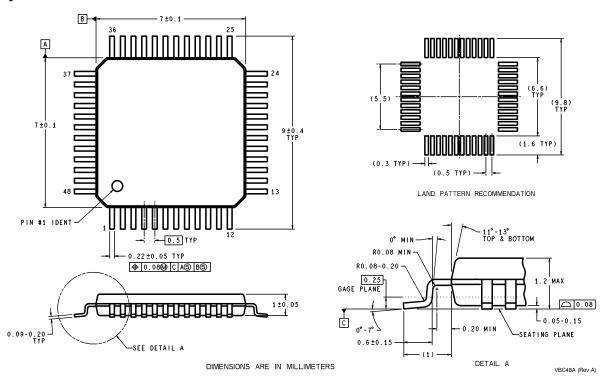

#### Physical Dimensions inches (millimeters) unless otherwise noted

Dimensions show in millimeters only Order Number DS90C241IVS, DS90C124IVS NS Package Number IVS48

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Tel: 81-3-5639-7560